Hai loại FET chính hiện đang tồn tại là: JFET và MOSFET.

MOSFET có thể được phân loại thêm thành loại cạn kiệt và loại nâng cao. Cả hai loại này đều xác định phương thức hoạt động cơ bản của MOSFET, trong khi bản thân thuật ngữ MOSFET là chữ viết tắt của bóng bán dẫn hiệu ứng trường-oxit-bán dẫn-kim loại.

Do thực tế là hai loại có các đặc tính hoạt động khác nhau, chúng tôi sẽ đánh giá từng loại riêng biệt trong các bài viết khác nhau.

Sự khác biệt giữa MOSFET Cải tiến và cạn kiệt

Về cơ bản, không giống như MOSFET nâng cao, MOSFET cạn kiệt ở trạng thái bật ngay cả khi có 0 V trên các thiết bị đầu cuối cổng-nguồn (VGS).

Đối với MOSFET nâng cao, điện áp cổng vào nguồn (VGS) phải cao hơn điện áp ngưỡng cổng vào nguồn (VGS (th)) để làm cho nó tiến hành .

Tuy nhiên, đối với MOSFET cạn kênh N, giá trị VGS (th) của nó trên 0 V. Điều này có nghĩa là ngay cả khi VGS = 0 V, MOSFET cạn kiệt vẫn có thể dẫn dòng. Để tắt nó, VGS của MOSFET cạn kiệt cần được giảm xuống dưới VGS (th) (âm).

Trong bài viết này, chúng ta sẽ thảo luận về loại cạn kiệt MOSFET, được cho là có các đặc điểm phù hợp với JFET. Sự giống nhau giữa điểm cắt và độ bão hòa gần IDSS.

Xây dựng cơ bản

Hình 5.23 cho thấy cấu trúc bên trong cơ bản của một MOSFET loại cạn kênh n.

Chúng ta có thể tìm thấy một khối vật liệu loại p được tạo ra bằng cách sử dụng đế silicon. Khối này được gọi là chất nền.

Chất nền là nền hoặc nền mà MOSFET được xây dựng trên đó. Đối với một số MOSFET, nó được liên kết nội bộ với thiết bị đầu cuối 'nguồn'. Ngoài ra, nhiều thiết bị cung cấp một đầu ra bổ sung ở dạng SS, có MOSFET 4 đầu cuối, như được tiết lộ trong Hình 5.23

Bộ thoát và cực nguồn được kết nối thông qua các tiếp điểm dẫn điện đến các vị trí pha tạp chất n, và được gắn qua một kênh n, như được chỉ ra trong cùng một hình.

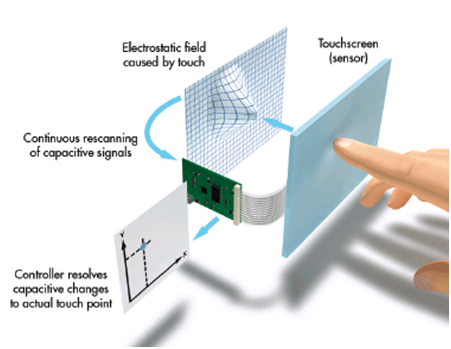

Cổng cũng được kết nối với một lớp kim loại, mặc dù nó được cách nhiệt với kênh n thông qua một lớp silicon dioxide mịn (SiOhai).

SiOhaisở hữu một dạng đặc tính cách điện độc đáo được gọi là chất điện môi tạo ra một điện trường đối lập trong chính nó để phản ứng với một điện trường tác dụng bên ngoài.

Là một lớp cách nhiệt, vật liệu SiOhaicung cấp cho chúng tôi những thông tin quan trọng sau:

Một sự cách ly hoàn toàn được phát triển giữa thiết bị đầu cuối cổng và kênh mosfet bằng vật liệu này.

Hơn nữa, đó là vì SiOhai, cổng của mosfet có thể có mức trở kháng đầu vào cực cao.

Do đặc tính trở kháng đầu vào cao quan trọng này, cổng hiện tại IGhầu như bằng không amps đối với bất kỳ cấu hình MOSFET phân cực một chiều nào.

Hoạt động cơ bản và đặc điểm

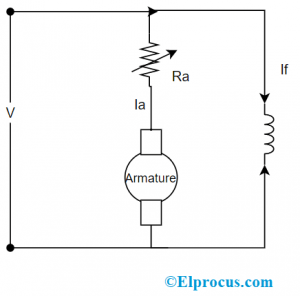

AS có thể được nhìn thấy trong hình 5.24, cổng vào điện áp nguồn đã được cấu hình ở 0 volt bằng cách kết nối hai đầu cuối với nhau, trong khi điện áp VDSđược áp dụng trên các thiết bị đầu cuối cống và nguồn.

Với thiết lập trên, phía cống thiết lập một điện thế dương bởi các điện tử tự do kênh n, cùng với một dòng điện tương đương qua kênh JFET. Ngoài ra, kết quả hiện tại VGS= 0V vẫn đang được xác định là IDSS, như được cho trong Hình 5.25

Chúng ta có thể thấy rằng trong hình 5.26 điện áp nguồn cổng VGSđược cung cấp một điện thế âm ở dạng -1V.

Điện thế âm này cố gắng đẩy các điện tử về phía nền kênh p (vì các điện tích đẩy nhau), và kéo các lỗ trống khỏi chất nền kênh p (vì các điện tích trái dấu hút nhau).

Tùy thuộc vào độ lệch âm V này lớn như thế nàoGSlà, sự tái kết hợp của các lỗ trống và các điện tử diễn ra dẫn đến sự khử các điện tử tự do trong kênh n có sẵn cho sự dẫn điện. Mức độ sai lệch âm tính cao hơn dẫn đến tỷ lệ tái tổ hợp cao hơn.

Do đó, dòng cống giảm khi điều kiện phân cực âm ở trên được tăng lên, điều này được chứng minh trong Hình 5.5 cho VGSmức độ VGS= -1, -2, v.v., cho đến khi vạch tắt của -6V.

Kết quả là dòng tiêu cùng với biểu đồ đường cong truyền tải giống như của một GIẤY TỜ.

Bây giờ, đối với V tích cựcGSgiá trị, cổng dương sẽ thu hút các điện tử dư thừa (hạt tải điện tự do) khỏi chất nền loại p, do dòng điện rò ngược. Điều này sẽ thiết lập các hạt tải điện mới bằng cách xảy ra va chạm giữa các hạt gia tốc.

Khi điện áp cổng vào nguồn có xu hướng tăng với tốc độ dương, dòng xả cho thấy sự gia tăng nhanh chóng, như được chứng minh trong Hình 5.5 vì những lý do tương tự như đã thảo luận ở trên.

Khoảng cách phát triển giữa các đường cong của VGS= 0V và VGS= +1 cho thấy rõ ràng lượng mà dòng điện tăng lên do biến thiên 1 - V của VGS

Do dòng xả tăng nhanh, chúng ta phải cẩn thận về định mức dòng điện tối đa, nếu không nó có thể vượt qua giới hạn điện áp cổng dương.

Ví dụ, đối với loại thiết bị được mô tả trong Hình 5.5, áp dụng chữ VGS= + 4V sẽ làm cho dòng xả tăng lên ở 22,2 mA, có thể vượt qua giới hạn đánh thủng tối đa (dòng điện) của thiết bị.

Điều kiện trên cho thấy rằng việc sử dụng điện áp cổng vào nguồn dương tạo ra hiệu ứng tăng cường đối với số lượng hạt tải điện tự do trong kênh, trái ngược với khi VGS= 0V.

Đây là lý do tại sao vùng điện áp cổng dương trên đặc tuyến cống hoặc chuyển đổi thường được gọi là khu vực nâng cao . Vùng này nằm giữa mức cắt và mức bão hòa của IDSShoặc vùng cạn kiệt.

Giải quyết một vấn đề ví dụ

Ưu điểm và Ứng dụng

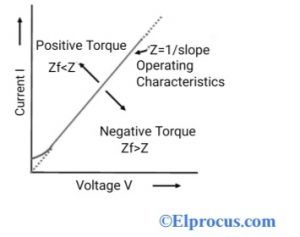

Trái ngược với MOSFET chế độ nâng cao, nơi chúng tôi thấy dòng xả giảm xuống 0 để đáp ứng với điện áp cổng vào nguồn bằng không, FET chế độ cạn kiệt hiện đại có dòng điện đáng chú ý với điện áp cổng bằng không. Nói một cách chính xác, điện trở nguồn từ nguồn thường là 100 Ohms ở điện áp bằng không.

Như được chỉ ra trong biểu đồ trên, rds điện trở BẬT(trên)so với dải tín hiệu tương tự trông giống như một phản ứng thực tế bằng phẳng. Đặc tính này, cùng với các mức điện dung thấp của thiết bị loại cạn kiệt nâng cao này, cho phép chúng đặc biệt lý tưởng làm công tắc tương tự cho các ứng dụng chuyển đổi âm thanh và video.

Thuộc tính 'normal-on' của MOSFET ở chế độ cạn kiệt cho phép thiết bị hoàn toàn phù hợp với các bộ điều chỉnh dòng FET đơn lẻ.

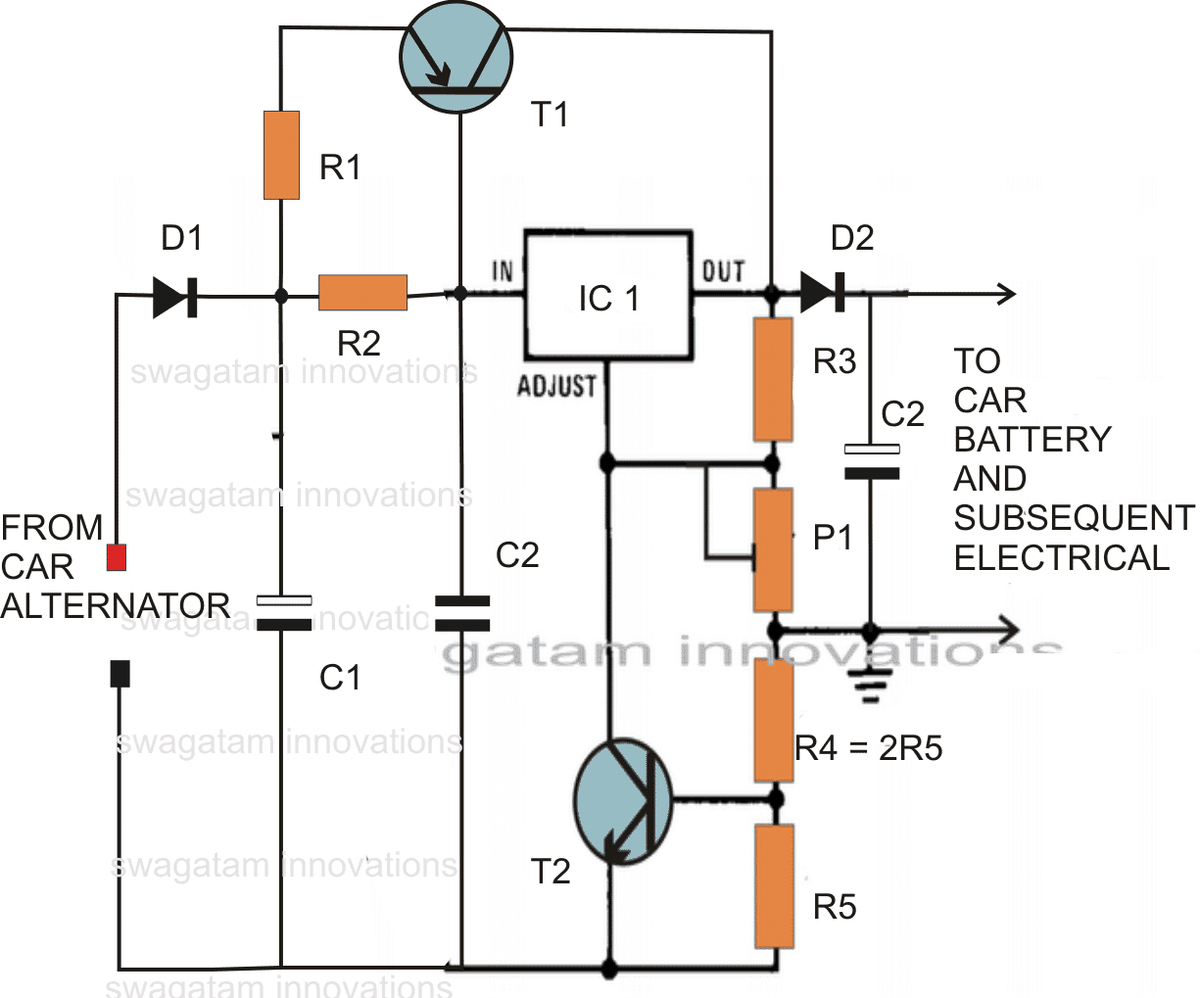

Một mạch ví dụ như vậy có thể được nhìn thấy trong hình sau.

Giá trị Rs có thể được xác định bằng công thức:

RS= VGStắt[1 - (TôiD/TÔIDSS)1/2] / TÔID

Ở đâu TôiD là lượng dòng điện điều chỉnh cần thiết ở đầu ra.

Ưu điểm chính của MOSFET chế độ cạn kiệt trong ứng dụng nguồn hiện tại là điện dung tiêu hao tối thiểu, điều này làm cho chúng thích hợp cho các ứng dụng phân cực trong mạch rò rỉ đầu vào thấp, tốc độ trung bình (> 50 V / us).

Hình bên dưới thể hiện bộ vi sai dòng điện rò rỉ đầu vào thấp sử dụng chức năng rò rỉ thấp kép FET.

Nói chung, một trong hai bên của JFET sẽ bị sai lệch ở ID = 500 uA. Do đó, dòng điện có thể đạt được để sạc bù và điện dung lạc trở nên bị hạn chế ở 2ID hoặc trong những trường hợp như thế này là 1,0 mA. Các tính năng tương ứng của JFET đã được sản xuất chứng minh và đảm bảo trên biểu dữ liệu.

Cs tượng trưng cho điện dung đầu ra của nguồn dòng 'đuôi' giai đoạn đầu vào. Điện dung này rất quan trọng trong các bộ khuếch đại không đảo, do thực tế là tầng đầu vào trải qua các trao đổi tín hiệu đáng kể trong toàn bộ mạng này và dòng sạc trong C có thể lớn. Trong trường hợp sử dụng nguồn dòng điện bình thường, điện dung đuôi này có thể là nguyên nhân gây ra sự suy giảm tốc độ đáng chú ý trong các mạch không đảo (so với các ứng dụng đảo, trong đó dòng sạc trong Cs có xu hướng nhỏ nhất).

Sự sụt giảm tỷ lệ quay vòng có thể được biểu thị bằng:

1 / 1+ (Cs / Sc)

Miễn là Cs thấp hơn Cc (tụ bù), có thể hầu như không có bất kỳ sự thay đổi nào trong tốc độ quay. Làm việc với DMOS FET, C có thể vào khoảng 2 pF. Chiến lược này tạo ra một sự cải thiện lớn về tỷ lệ quay vòng. Khi cần dòng điện thâm hụt cao hơn 1 đến 5 mA, thiết bị có thể được chuyển sang chế độ nâng cao để tạo ra tới 20 mA cho VGS tối đa là + 2,5 V, với điện dung đầu ra tối thiểu tiếp tục là một khía cạnh quan trọng.

Ứng dụng tiếp theo bên dưới thể hiện một mạch nguồn dòng chế độ nâng cao thích hợp.

Một công tắc tương tự 'bình thường-trên' có thể được chế tạo cho các yêu cầu khi điều kiện tiêu chuẩn trở nên cần thiết khi xảy ra sự cố điện áp nguồn, ví dụ trong các loại công cụ thử nghiệm tự động hoặc để đảm bảo khởi động chính xác các mạch logic khi công tắc BẬT.

Điện áp ngưỡng âm giảm của thiết bị cung cấp các điều kiện tiên quyết về ổ đĩa cơ bản và cho phép hoạt động với điện áp tối thiểu.

Mạch bên dưới minh họa các yếu tố thiên vị phổ biến cho bất kỳ công tắc tương tự DMOS chế độ cạn kiệt nào.

Để tắt thiết bị, cần có điện áp âm trên cổng. Phải nói rằng, điện trở bật có thể được giảm thiểu khi FET được tăng cường thêm bằng cách sử dụng điện áp cổng dương, cho phép nó hoạt động cụ thể trong vùng chế độ nâng cao cùng với vùng chế độ cạn kiệt.

Phản hồi này có thể được chứng kiến trong biểu đồ sau.

Mức tăng tần số cao của thiết bị, cùng với các giá trị điện dung thấp của nó, mang lại 'con số đáng giá' tăng lên. Nó thực sự là một yếu tố quan trọng trong khuếch đại VHF và UHF, chỉ định sản phẩm băng thông khuếch đại (GBW) của FET, có thể được mô tả là:

GBW = gfs / 2 Số Pi (Ctrong+ Cngoài)

MOSFET loại cạn kiệt kênh p

Việc xây dựng MOSFET loại suy giảm kênh p là một sự đảo ngược hoàn hảo của phiên bản kênh n được trình bày trong Hình 5.23. Có nghĩa là, chất nền bây giờ có dạng n-type và kênh trở thành dạng p, như có thể thấy trong Hình 5.28a bên dưới.

Nhận dạng đầu cuối vẫn không thay đổi, nhưng các cực tính của điện áp và dòng điện được đảo ngược, như được chỉ ra trong cùng một hình. Các đặc tính cống sẽ chính xác như được mô tả trong Hình 5.5, ngoại trừ VDSdấu mà trong trường hợp này sẽ nhận giá trị âm.

Dòng cống IDcho thấy một cực tích cực trong trường hợp này, đó là bởi vì chúng ta đã đảo ngược hướng của nó. VGScho thấy một cực ngược lại, điều này có thể hiểu được, như được chỉ ra trong Hình 5.28c.

Vì VGSđược đảo ngược tạo ra một hình ảnh phản chiếu cho các đặc tính truyền như được chỉ ra trong Hình 5,28b.

Có nghĩa là, dòng chảy tăng trong V dươngGSvùng từ điểm cắt tại VGS= Vp cho đến khi tôiDSS, sau đó nó tiếp tục tăng lên khi giá trị âm của VGSmọc.

Ký hiệu

Các dấu hiệu đồ họa cho MOSFET loại suy giảm kênh n và kênh p có thể được chứng kiến trong Hình 5.29 ở trên.

Quan sát cách các biểu tượng được chọn nhằm thể hiện cấu trúc thực của thiết bị.

Việc không có kết nối trực tiếp (vì cách điện cổng) giữa cổng và kênh được ký hiệu bằng khoảng cách giữa cổng và các đầu cuối khác nhau của ký hiệu.

Đường thẳng đứng thể hiện kênh được gắn giữa cống và nguồn và được 'giữ' bởi chất nền.

Hai nhóm ký hiệu được cung cấp trong hình trên cho mỗi loại kênh để làm nổi bật thực tế là trong một số thiết bị, bề mặt có thể được tiếp cận từ bên ngoài trong khi ở những thiết bị khác, điều này có thể không được nhìn thấy.

MOSFET (Loại cải tiến)

Mặc dù loại suy giảm và loại tăng cường MOSFET trông giống nhau về cấu trúc bên trong và chế độ chức năng, nhưng đặc điểm của chúng có thể khá khác nhau.

Sự khác biệt chính là dòng xả phụ thuộc vào mức điện áp cổng vào nguồn cụ thể cho hành động cắt.

Chính xác là MOSFET loại nâng cao kênh n có thể hoạt động với điện áp nguồn / cổng dương, thay vì một loạt các điện thế âm thường có thể tác động đến MOSFET loại cạn kiệt.

Xây dựng cơ bản

Bạn có thể hình dung MOSFET loại nâng cao kênh n như sau

Hình 5.31.

Phần vật liệu loại p được tạo ra thông qua đế silicon, và như đã học trước đây nó được gọi là chất nền.

Chất nền này trong một số trường hợp được gắn bên trong với chân nguồn trong MOSFET loại cạn kiệt, trong khi trong một số trường hợp, nó được kết thúc như một dây dẫn thứ tư để cho phép kiểm soát bên ngoài mức tiềm năng của nó.

Các đầu nối nguồn và đầu nối thoát nước như bình thường được nối bằng cách sử dụng các tiếp điểm kim loại với các vùng pha tạp chất n.

Tuy nhiên, điều quan trọng là phải hình dung rằng trong Hình 5.31 kênh giữa hai vùng pha tạp n bị thiếu.

Đây có thể được coi là sự khác biệt cơ bản giữa cách bố trí bên trong của MOSFET loại cạn kiệt và loại nâng cao, đó là sự vắng mặt của một kênh cố hữu được cho là một phần của thiết bị.

Lớp SiO2 có thể được nhìn thấy vẫn còn phổ biến, đảm bảo sự cách ly giữa đế kim loại của thiết bị đầu cuối cổng và khu vực giữa cống và nguồn. Tuy nhiên, ở đây nó có thể được chứng kiến đứng tách biệt khỏi phần vật liệu loại p.

Từ cuộc thảo luận ở trên, chúng ta có thể kết luận rằng cách bố trí bên trong MOSFET cạn kiệt và nâng cao có thể có một số điểm tương đồng, ngoại trừ kênh bị thiếu giữa nguồn / nguồn đối với loại MOSFET nâng cao.

Hoạt động cơ bản và đặc điểm

Đối với MOSFET loại nâng cao khi 0 V được đưa vào VGS của nó, do thiếu kênh n (được biết là mang rất nhiều hạt tải điện tự do) khiến đầu ra hiện tại bằng 0, điều này hoàn toàn không giống với loại cạn kiệt của MOSFET, có ID = IDSS.

Trong tình huống như vậy do thiếu một đường dẫn qua các cực thoát / nguồn, một lượng lớn hạt tải điện ở dạng electron không thể tích tụ tại cống / nguồn (vì các vùng pha tạp n).

Áp dụng một số điện thế dương ở VDS, với VGS được đặt ở 0 volt và đầu cuối SS được nối tắt với đầu cuối nguồn, chúng tôi thực sự tìm thấy một vài điểm nối pn phân cực ngược giữa vùng pha tạp n và chất nền p để cho phép bất kỳ sự dẫn truyền đáng chú ý nào qua cống về nguồn.

Trong hình 5.32 cho thấy một điều kiện trong đó VDS và VGS được áp dụng với một số điện áp dương cao hơn 0 V, cho phép cống và cổng ở điện thế dương đối với nguồn.

Điện thế dương tại cổng đẩy các lỗ trên chất nền p dọc theo cạnh của lớp SiO2 rời khỏi vị trí và đi sâu hơn vào các vùng của chất nền p, như thể hiện trong hình trên. Điều này xảy ra do các điện tích tương tự đẩy nhau.

Điều này dẫn đến một vùng cạn kiệt được tạo ra gần với lớp cách điện SiO2 là khoảng trống của các lỗ.

Mặc dù vậy, các điện tử của chất nền p là hạt tải điện thiểu số của vật liệu được kéo về phía cổng dương và bắt đầu tập hợp lại trong vùng gần với bề mặt của lớp SiO2.

Do tính chất cách nhiệt của các hạt tải điện âm lớp SiO2 cho phép các hạt tải điện âm không bị hấp thụ ở thiết bị đầu cuối cổng.

Khi chúng ta tăng mức VGS, mật độ điện tử gần bề mặt SiO2 cũng tăng lên, cho đến khi vùng loại n cảm ứng cuối cùng có thể cho phép dẫn truyền có thể định lượng qua cống / nguồn.

Độ lớn VGS gây ra sự gia tăng tối ưu trong dòng xả được gọi là điện áp ngưỡng, được ký hiệu bằng ký hiệu VT . Trong biểu dữ liệu, bạn sẽ có thể thấy đây là VGS (Th).

Như đã học ở trên, do không có kênh ở VGS = 0 và được 'tăng cường' với ứng dụng điện áp cổng-nguồn tích cực, loại MOSFET này được gọi là MOSFET loại nâng cao.

Bạn sẽ thấy rằng cả MOSFET loại cạn kiệt và loại tăng cường đều thể hiện các vùng loại tăng cường, nhưng thuật ngữ sự nâng cao được sử dụng cho cái sau vì nó hoạt động cụ thể bằng cách sử dụng chế độ hoạt động nâng cao.

Bây giờ, khi VGS được đẩy qua giá trị ngưỡng, nồng độ của các hạt tải điện tự do sẽ tăng lên trong kênh mà nó được tạo ra. Điều này làm cho dòng chảy tăng lên.

Mặt khác, nếu chúng ta giữ VGS không đổi và tăng mức VDS (điện áp nguồn vào), điều này cuối cùng sẽ khiến MOSFET đạt đến điểm bão hòa, như thường lệ cũng xảy ra với bất kỳ JFET nào hoặc MOSFET cạn kiệt.

Như được minh họa trong Hình 5.33, ID dòng xả được làm phẳng với sự hỗ trợ của quá trình chụm lại, được chỉ ra bởi kênh hẹp hơn về phía cuối cống của kênh cảm ứng.

Bằng cách áp dụng định luật điện áp Kirchhoff cho các điện áp đầu cuối của MOSFET trong Hình 5.33, chúng tôi nhận được:

Nếu VGS được giữ không đổi đến một giá trị cụ thể, ví dụ 8 V và VDS được tăng từ 2 lên 5 V, thì điện áp VDG bằng Eq. 5.11 có thể được nhìn thấy giảm từ -6 xuống -3 V, và điện thế cổng ngày càng kém tích cực hơn so với điện áp cống.

Đáp ứng này cấm các hạt tải điện hoặc electron tự do bị kéo về phía vùng này của kênh cảm ứng, do đó dẫn đến giảm chiều rộng hiệu dụng của kênh.

Cuối cùng, độ rộng kênh giảm đến mức pinch-off, đạt đến điều kiện bão hòa tương tự như những gì chúng ta đã học trong bài báo MOSFET cạn kiệt trước đó của chúng tôi.

Có nghĩa là, việc tăng VDS thêm nữa với một VGS cố định không ảnh hưởng đến mức bão hòa của ID, cho đến khi đạt đến tình huống hỏng hóc.

Nhìn vào Hình 5.34, chúng ta có thể xác định rằng đối với một MOSFET như trong Hình 5.5 có VGS = 8 V, bão hòa diễn ra ở mức VDS là 6 V. Nói chính xác mức bão hòa VDS được liên kết với mức VGS được áp dụng bằng cách:

Không nghi ngờ gì nữa, do đó, nó ngụ ý rằng khi giá trị VT được cố định, việc tăng mức VGS sẽ gây ra các mức bão hòa cao hơn cho VDS thông qua quỹ tích của các mức bão hòa.

Đề cập đến các đặc tính thể hiện trong hình trên, mức VT là 2 V, điều này được thể hiện rõ ràng bằng thực tế là dòng cống đã giảm xuống 0 mA.

Do đó, chúng ta thường có thể nói:

Khi các giá trị VGS nhỏ hơn mức ngưỡng đối với MOSFET loại nâng cao, dòng xả của nó là 0 mA.

Chúng ta cũng có thể thấy rõ trong hình trên rằng miễn là VGS được nâng cao hơn từ VT đến 8 V, mức bão hòa tương ứng cho ID cũng tăng từ mức 0 đến mức 10 mA.

Hơn nữa, chúng ta có thể nhận thấy thêm rằng không gian giữa các mức VGS tăng lên khi giá trị của VGS tăng lên, gây ra sự gia tăng vô hạn trong dòng chảy.

Chúng tôi nhận thấy giá trị dòng xả có liên quan đến điện áp cổng vào nguồn cho các mức VGS lớn hơn VT, thông qua mối quan hệ phi tuyến sau:

Thuật ngữ được hiển thị trong dấu ngoặc vuông là thuật ngữ chịu trách nhiệm về mối quan hệ phi tuyến giữa ID và VGS.

Số hạng k là một hằng số và là một hàm của bố cục MOSFET.

Chúng ta có thể tìm giá trị của hằng số k này qua phương trình sau:

trong đó ID (bật) và VGD (bật) là các giá trị cụ thể tùy thuộc vào đặc tính của thiết bị.

Trong hình 5.35 tiếp theo, chúng tôi thấy các đặc tính thoát nước và chuyển tải được sắp xếp cạnh nhau để làm rõ quá trình chuyển tải qua nhau.

Về cơ bản, nó tương tự như quy trình đã giải thích trước đây cho JFET và MOSFET loại cạn kiệt.

Tuy nhiên, đối với trường hợp hiện tại, chúng ta phải nhớ rằng dòng xả là 0 mA đối với VGS VT.

Ở đây ID có thể thấy một lượng dòng điện đáng chú ý, dòng điện này sẽ tăng lên khi được xác định bởi Eq. 5.13.

Lưu ý, trong khi xác định các điểm trên các đặc tính truyền từ các đặc tính cống, chúng tôi chỉ xem xét các mức bão hòa. Điều này hạn chế khu vực hoạt động ở các giá trị VDS cao hơn mức bão hòa như được thiết lập bởi Eq. (5.12).

MOSFET loại cải tiến kênh p

Cấu trúc của MOSFET loại tăng cường kênh p như trong Hình 5.37a hoàn toàn ngược lại với cấu trúc hiển thị trong Hình 5.31.

Có nghĩa là, bây giờ bạn thấy rằng một chất nền loại n và các vùng pha tạp p bên dưới các mối nối cống và nguồn.

Các đầu nối tiếp tục được thiết lập như đã thiết lập, nhưng mỗi hướng dòng điện và cực tính điện áp đều bị đảo ngược.

Các đặc điểm của cống có thể trông giống như được cho trong Hình 5.37c, có lượng dòng điện ngày càng tăng do cường độ âm liên tục của VGS.

Các đặc điểm truyền sẽ là ấn tượng phản chiếu (xung quanh trục ID) của đường cong truyền của Hình 5.35, có ID tăng với ngày càng nhiều giá trị âm của VGS trên VT, như được hiển thị trong Hình 5.37b. Các phương trình (5.11) đến (5.14) tương tự thích hợp với các thiết bị kênh p.

Người giới thiệu:

- https://en.wikipedia.org/wiki/MOSFET

- https://hi.wikipedia.org/wiki/%E0%A4%AE%E0%A5%89%E0%A4%B8%E0%A4%AB%E0%A5%87%E0%A4%9F

Một cặp: Mạch dò RF chống gián điệp - Máy dò lỗi không dây Tiếp theo: Đặc điểm chuyển giao