Trước đó, thiết kế của mạch logic có thể được thực hiện bằng cách sử dụng SSI (tích hợp quy mô nhỏ) các thành phần như cổng logic, bộ ghép kênh , de-multiplexers, FFs, vv Nhưng, bây giờ PLD có thể thay thế tất cả các thành phần SSI này. Vì vậy, đây là lý do để giảm ngành SSI so với PLD, và chúng được sử dụng trong một số ứng dụng. Các thiết bị logic có thể lập trình hoặc PLD là một loại chip được sử dụng để thực hiện mạch logic. Nó bao gồm một tập hợp các phần tử mạch logic có thể được sửa đổi theo một số cách. PLD trông giống như một hộp đen bao gồm các công tắc có thể lập trình cũng như các cổng logic. Chức năng chính của công tắc là cho phép các cổng logic trong PLD được liên kết với nhau để thực hiện các mạch logic. PLD được phân thành nhiều loại khác nhau như SPLD-simple PLD ( PLA & PAL ), CPLD-PLD phức tạp , FPGA- lĩnh vực cổng có thể lập trình . Bài viết này thảo luận về PAL và PLA là gì, thiết kế và sự khác biệt của chúng.

PAL và PLA là gì?

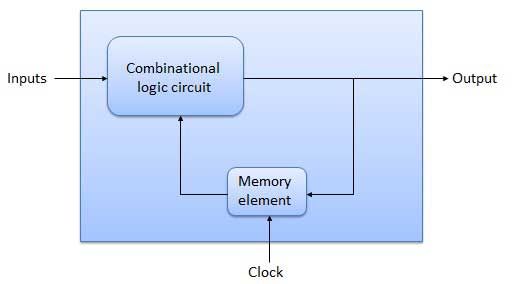

Cả hai Logic mảng có thể lập trình và Mảng logic có thể lập trình là các loại PLD (thiết bị logic có thể lập trình), và chúng chủ yếu được sử dụng để thiết kế logic kết hợp lẫn nhau theo logic tuần tự. Sự khác biệt chính giữa hai điều này là PAL có thể được thiết kế với một tập hợp các cổng VÀ và tập hợp cố định các cổng OR trong khi PLA có thể được thiết kế với một mảng AND có thể lập trình được mặc dù một tập hợp cố định của cổng OR. Thiết bị logic có thể lập trình cung cấp thiết kế mạch logic linh hoạt và đơn giản.

Logic mảng có thể lập trình

Trước các thiết bị logic có thể lập trình, mạch logic tổ hợp có thể được thiết kế với bộ ghép kênh, và các mạch này cũng cứng như hợp chất, sau đó PLD được phát triển. Thiết bị logic có thể lập trình ban đầu là ROM, nhưng nó đã không thành công do các vấn đề lãng phí phần cứng cũng như tăng cường phát triển theo cấp số nhân trong mọi ứng dụng phần cứng. Để khắc phục vấn đề này, PAL và PLA đã được sử dụng. Cả hai đều có thể lập trình và sử dụng hiệu quả phần cứng.

Mảng logic có thể lập trình

Thiết kế lôgic mảng có thể lập trình (PAL)

Các định nghĩa của thuật ngữ PAL hoặc Logic mảng có thể lập trình là một loại PLD được gọi là mạch Thiết bị logic có thể lập trình và hoạt động của PAL này cũng giống như PLA. Việc thiết kế logic mảng lập trình có thể được thực hiện với các cổng OR cố định cũng như các cổng AND có thể lập trình được. Bằng cách sử dụng điều này, chúng ta có thể triển khai hai hàm dễ dàng ở bất cứ nơi nào các cổng AND kết hợp với mỗi cổng HOẶC biểu thị số lượng điều kiện sản phẩm cao nhất có thể được tạo ra dưới dạng SOP (tổng sản phẩm) của một chức năng chính xác.

Khi các cổng logic như AND được kết nối liên tục về phía các cổng OR, và điều đó chỉ ra rằng thuật ngữ sản phẩm được sản xuất không được phân phối với các chức năng đầu ra. Ý tưởng chính đằng sau sự phát triển PLD là chế tạo logic Boolean phức hợp trên một chip duy nhất bằng cách loại bỏ hệ thống dây điện bị lỗi, tránh thiết kế logic, cũng như giảm tiêu thụ điện năng.

Ví dụ về PAL

Thực hiện những điều sau Biểu thức Boolean với sự giúp đỡ của logic mảng có thể lập trình (PAL)

X = AB + AC '

Y = AB ’+ BC’

Ở trên đưa ra hai Các hàm boolean ở dạng SOP (tổng sản phẩm) . Các thuật ngữ tích có trong biểu thức Boolean là X & Y và một thuật ngữ tích là AC ’thường gặp trong mọi phương trình. Vì vậy, tổng số cổng logic cần thiết để tạo ra hai phương trình trên là cổng VÀ-4 HOẶC cổng-2 có thể lập trình được. Sơ đồ logic PAL tương đương được hiển thị bên dưới.

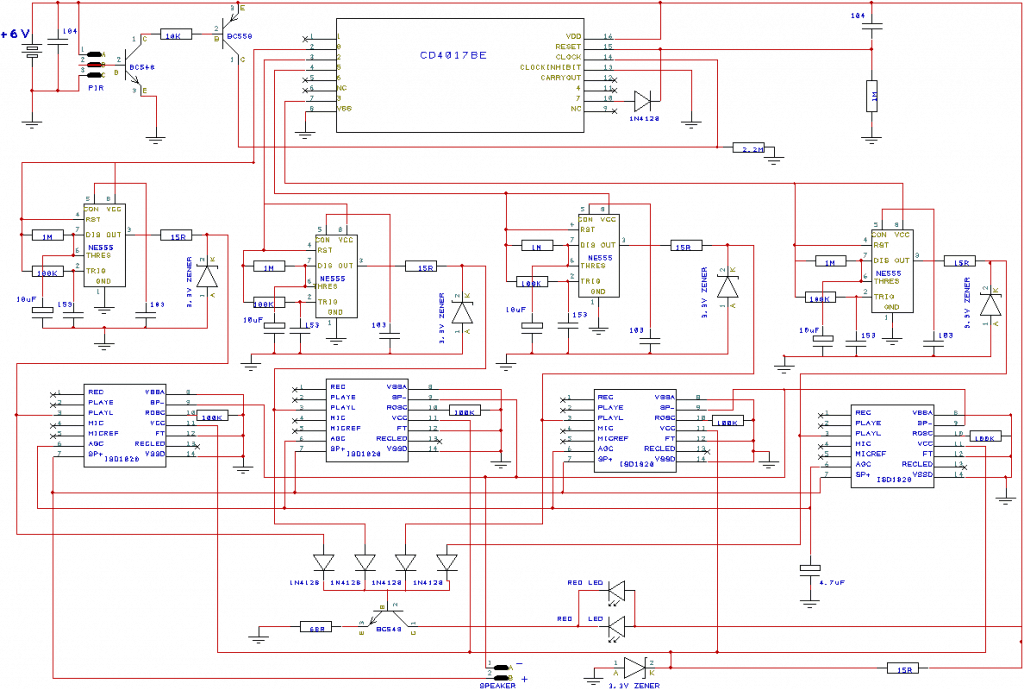

Mạch logic PAL

Các cổng AND có thể lập trình được có quyền nhập cho các đầu vào biến bình thường cũng như bổ sung. Trong sơ đồ logic trên, các đầu vào có sẵn cho mỗi cổng AND là A, A ’, B, B’, C, C ’. Vì vậy, để tạo một thuật ngữ sản phẩm duy nhất với mọi cổng AND, chương trình là bắt buộc.

Tất cả các điều khoản sản phẩm có thể đạt được tại đầu vào của mỗi cổng OR. Ở đây, các kết nối có thể lập trình trên cổng logic có thể được ký hiệu bằng ký hiệu ‘X’.

Ở đây, các đầu vào cổng OR được cố định. Do đó, các điều khoản sản phẩm bắt buộc được liên kết với mỗi đầu vào cổng OR. Kết quả là, các cổng này sẽ tạo ra các phương trình Boolean cụ thể. Các '.' Biểu tượng đại diện cho các kết nối vĩnh viễn.

Thiết kế mảng logic có thể lập trình (PLA)

Định nghĩa của thuật ngữ PLA trình bày hàm Boolean ở dạng tổng tích (SOP). Việc thiết kế mảng logic có thể lập trình này có thể được thực hiện bằng cách sử dụng các cổng logic như AND, OR và NOT bằng cách chế tạo trên chip, giúp mọi đầu vào cũng như lời khen của nó đều có thể đạt được đối với mọi cổng AND.

Mọi đầu ra của cổng VÀ được kết nối với mọi cổng OR. Cuối cùng, đầu ra của cổng OR tạo ra đầu ra của chip. Vì vậy, đây là cách một kết hợp thích hợp được hoàn thành để sử dụng các biểu thức của tổng của tích. Trong mảng logic có thể lập trình, các kết nối của cổng logic như AND & OR có thể lập trình được. PLA đắt và khó so sánh với PAL. PAL sử dụng hai phương pháp được phát triển khác nhau có thể được sử dụng cho mảng logic có thể lập trình để nâng cao tính dễ dàng trong lập trình. Trong loại phương pháp này, mọi kết nối có thể được thực hiện bằng cách sử dụng cầu chì trên mỗi điểm giao nhau ở bất cứ nơi nào có thể tháo rời các kết nối không cần thiết bằng cách thổi cầu chảy. Kỹ thuật cuối cùng bao gồm việc tạo kết nối trong khi quá trình chế tạo sử dụng vỏ bọc phù hợp được cung cấp cho mô hình kết nối chính xác.

Ví dụ về PLA

Triển khai biểu thức Boolean sau với sự trợ giúp của mảng logic có thể lập trình (PLA)

X = AB + AC '

Y = AB '+ BC + AC'

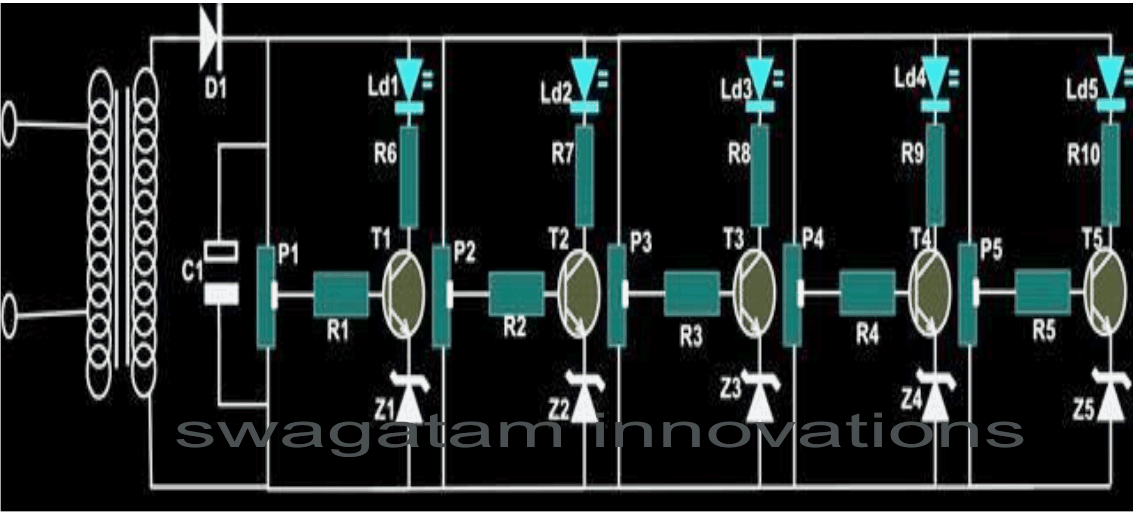

Hai hàm Boolean đã cho ở trên có dạng SOP (tổng tích). Các thuật ngữ tích có trong biểu thức Boolean là X & Y và một thuật ngữ tích là AC ’thường gặp trong mọi phương trình. Vì vậy, tổng số cổng logic cần thiết để tạo ra hai phương trình trên là cổng VÀ-4, HOẶC có thể lập trình được hoặc cổng-2. Sơ đồ logic PLA tương đương được hiển thị bên dưới.

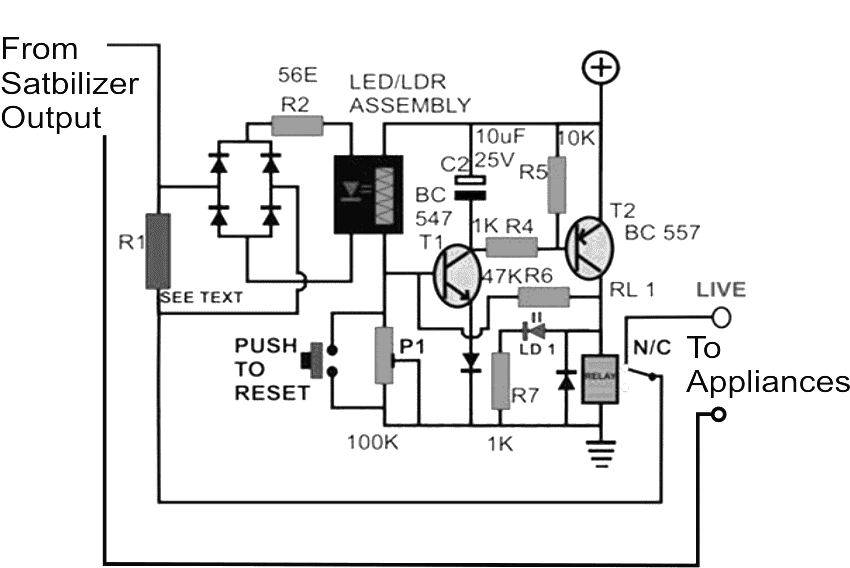

Mạch logic PLA

Các cổng AND có thể lập trình được có quyền nhập cho các đầu vào biến bình thường cũng như bổ sung. Trong sơ đồ logic trên, các đầu vào có sẵn cho mỗi cổng AND là A, A ’, B, B’, C, C ’. Vì vậy, để tạo một thuật ngữ sản phẩm duy nhất với mọi cổng AND, chương trình là bắt buộc.

Tất cả các điều khoản sản phẩm có thể đạt được ở đầu vào của mỗi cổng OR. Ở đây, các kết nối có thể lập trình trên cổng logic có thể được ký hiệu bằng ký hiệu ‘X’.

Sự khác biệt giữa PAL và PLA

Các Sự khác biệt giữa PAL và PLA trong Biểu mẫu bảng chủ yếu bao gồm PAL và PLA dạng đầy đủ , xây dựng, tính khả dụng, tính linh hoạt, chi phí, số lượng chức năng và tốc độ được thảo luận bên dưới.

| Logic mảng có thể lập trình (PAL) | Mảng logic có thể lập trình (PLA) |

| Dạng đầy đủ của PAL là logic mảng có thể lập trình được | Dạng đầy đủ của PLA là một mảng logic có thể lập trình được |

| Việc xây dựng PAL có thể được thực hiện bằng cách sử dụng bộ sưu tập cổng VÀ & HOẶC có thể lập trình | Việc xây dựng PLA có thể được thực hiện bằng cách sử dụng bộ sưu tập AND & bộ sưu tập cố định các cổng OR có thể lập trình được. |

| Sự sẵn có của PAL ít sung mãn hơn | Tính khả dụng của PLA nhiều hơn |

| Tính linh hoạt của lập trình PAL hơn | Tính linh hoạt của PLA kém hơn |

| Chi phí của một PAL đắt | Chi phí của PLA là tầm trung |

| Số lượng các chức năng được thực hiện trong PAL là lớn | Số lượng các chức năng được thực hiện trong PLA bị hạn chế |

| Tốc độ của PAL chậm | Tốc độ của PLA cao |

Vì vậy, đây là tất cả về PAL và PLA. Từ thông tin trên, cuối cùng, chúng ta có thể kết luận rằng đây là các thiết bị logic có thể lập trình (PLD), nơi mảng logic có thể lập trình linh hoạt hơn logic mảng có thể lập trình. Tuy nhiên, logic mảng có thể lập trình có thể dễ dàng tạo ra một mạch logic tổ hợp. Đây là một câu hỏi dành cho bạn, vai trò của PAL và PLA trong Điện tử Kỹ thuật số ?