Quá trình thiết kế phần cứng kỹ thuật số đã chuyển đổi mạnh mẽ trong vài năm qua. Vì vậy, các mạch kỹ thuật số nhỏ có thể được thực hiện bằng cách sử dụng PAL và PLA. Mỗi thiết bị được sử dụng để thực hiện các mạch khác nhau không cần nhiều hơn số i / ps, o / ps và các điều khoản sản phẩm được cung cấp trong chip cụ thể. Những con chip này có kích thước không đủ đến khá khiêm tốn, thường hỗ trợ một số lượng đầu vào và đầu ra lẫn nhau không quá 32. Để thiết kế các mạch này cần nhiều đầu vào và đầu ra hơn, có thể sử dụng nhiều PLA / PAL hoặc loại khác đẳng cấp hơn của chip có thể được sử dụng được gọi là CPLD (thiết bị logic lập trình phức tạp). Một chip CPLD bao gồm một số khối mạch trên một chip duy nhất với các tài nguyên dây bên trong để gắn các khối mạch. Mỗi khối mạch có thể so sánh với PLA hoặc PAL.

Thiết bị logic có thể lập trình phức tạp là gì?

Từ viết tắt của CPLD là 'Các thiết bị logic có thể lập trình phức tạp', nó là một loại mạch tích hợp mà các nhà thiết kế ứng dụng thiết kế để triển khai phần cứng kỹ thuật số như điện thoại di động. Chúng có thể xử lý các thiết kế cao hơn có chủ đích so với SPLD (thiết bị logic có thể lập trình đơn giản), nhưng cung cấp ít logic hơn FPGA ( lĩnh vực cổng có thể lập trình ) .CPLD bao gồm nhiều khối logic, mỗi khối bao gồm 8-16 macrocell. Bởi vì mỗi khối logic thực hiện một chức năng cụ thể, tất cả các macrocell trong khối logic đều được kết nối đầy đủ. Tùy thuộc vào việc sử dụng, các khối này có thể được kết nối với nhau hoặc không.

Thiết bị logic có thể lập trình phức tạp

Hầu hết các CPLD (thiết bị logic có thể lập trình phức tạp) đều có macrocell với tổng hàm logic và chức năng tự chọn FF (lật ngược) . Tùy thuộc vào chip, chức năng logic tổ hợp hỗ trợ từ 4 đến 16 điều khoản sản phẩm với quạt trong bao gồm. CPLD cũng khác nhau về thanh ghi dịch chuyển và cổng logic. Vì lý do này, CPLD có số lượng cổng logic lớn có thể được sử dụng thay vì FPGA. Một thông số kỹ thuật CPLD khác biểu thị số lượng điều khoản sản phẩm mà macrocell có thể thực hiện. Các thuật ngữ sản phẩm là sản phẩm của các tín hiệu kỹ thuật số thực hiện một chức năng logic cụ thể.

CPLD có sẵn ở một số dạng gói IC và họ logic. Các CPLD cũng khác nhau về điện áp cung cấp, dòng điện hoạt động, dòng điện dự phòng và công suất tiêu tán. Ngoài ra, chúng có thể đạt được với nhiều bộ nhớ khác nhau và nhiều loại hỗ trợ bộ nhớ khác nhau. Thông thường, bộ nhớ được biểu thị bằng bit / megabit. Hỗ trợ bộ nhớ bao gồm ROM, RAM và RAM cổng kép. Nó cũng bao gồm CAM (bộ nhớ địa chỉ nội dung) cũng như bộ nhớ FIFO (đầu vào, đầu ra) và bộ nhớ LIFO (cuối cùng vào, cuối ra).

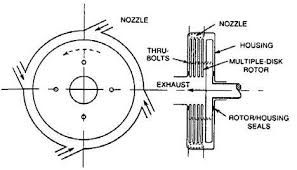

Kiến trúc của thiết bị logic có thể lập trình phức tạp

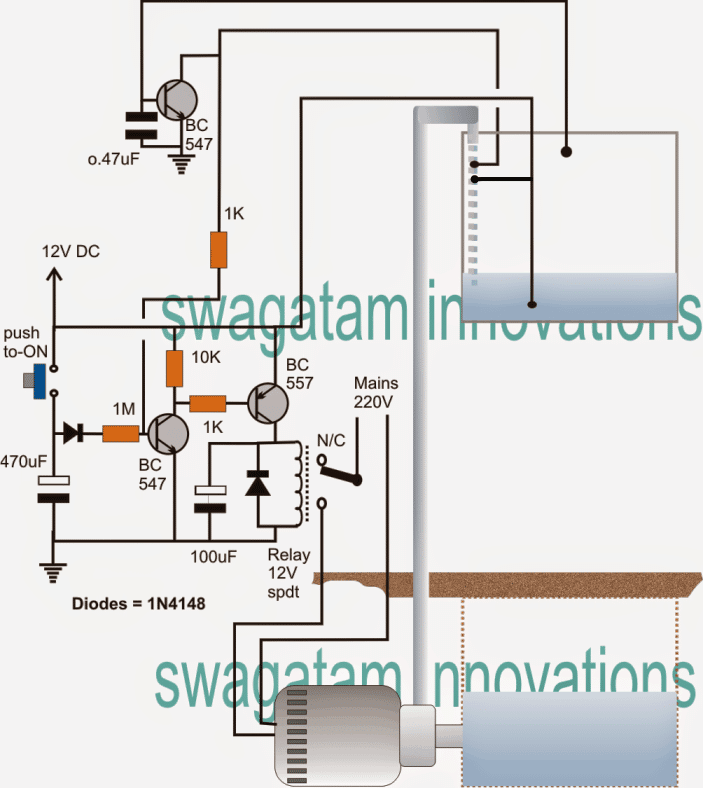

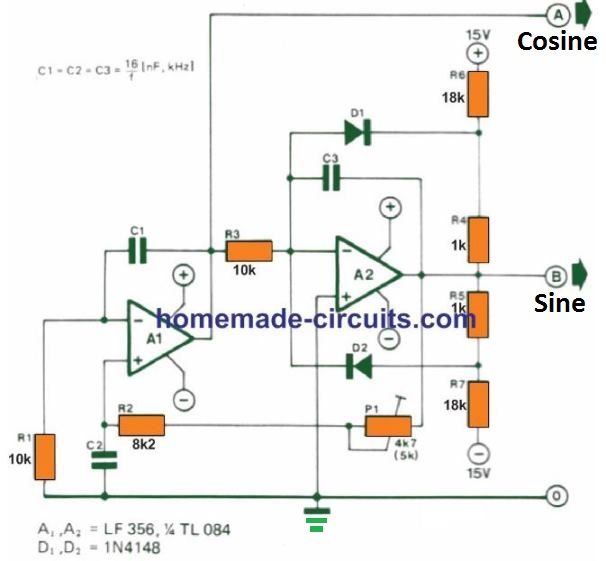

Một thiết bị logic có thể lập trình phức tạp bao gồm một nhóm các FB có thể lập trình được (các khối chức năng). Các đầu vào và đầu ra của các khối chức năng này được kết nối với nhau bằng một GIM (ma trận kết nối toàn cầu). Ma trận kết nối này có thể cấu hình lại, để chúng ta có thể sửa đổi các điểm tiếp xúc giữa các khối chức năng. Sẽ có một số khối đầu vào và đầu ra cho phép chúng ta hợp nhất CPLD với thế giới bên ngoài. Kiến trúc của CPLD được hiển thị bên dưới.

Nói chung, FB có thể lập trình trông giống như mảng cổng logic , trong đó một dãy cổng AND có thể được lập trình và cổng OR ổn định. Tuy nhiên, mỗi nhà sản xuất có cách suy nghĩ của họ để thiết kế khối chức năng. Có thể tìm thấy o / p được liệt kê bằng cách vận hành các tín hiệu phản hồi thu được từ các đầu ra cổng OR.

Kiến trúc CPLD

Trong lập trình CPLD, lần đầu tiên thiết kế được mã hóa bằng ngôn ngữ Verilog hoặc VHDL sau khi mã được (mô phỏng và tổng hợp. Trong quá trình tổng hợp, mô hình CPLD (thiết bị đích) được chọn thủ công và danh sách lưới ánh xạ dựa trên công nghệ được tạo ra. Danh sách này có thể đóng -phù hợp với kiến trúc CPLD chính hãng bằng cách sử dụng quy trình địa điểm và tuyến đường, thường đạt được bằng phần mềm xác định vị trí và tuyến đường thuộc quyền sở hữu của Công ty CPLD. Sau đó, nhà điều hành sẽ thực hiện một số quy trình xác nhận. Nếu mọi thứ tốt, anh ta sẽ sử dụng CPLD, nếu không anh ấy sẽ sắp xếp lại nó.

Các vấn đề về kiến trúc của CPLD

Khi xem xét một thiết bị logic có thể lập trình phức tạp để sử dụng trong thiết kế, có một số vấn đề về kiến trúc sau đây có thể được tính đến

- Công nghệ lập trình

- Khả năng khối chức năng

- Khả năng I / O

Một số họ CPLD từ các nhà bán lẻ khác nhau bao gồm

- Gia đình Altera MAX 7000 và MAX 9000

- Atmel ATF và ATV họ

- Họ mạng isp LSI

- Họ mạng lưới (Vantis) MACH

- Họ Xilinx XC9500

Các gia đình của CPLD

Các ứng dụng của CPLD

Các ứng dụng của CPLD bao gồm những điều sau đây

- Các thiết bị logic lập trình phức tạp là lý tưởng cho các ứng dụng điều khiển quan trọng, hiệu suất cao.

- CPLD có thể được sử dụng trong các thiết kế kỹ thuật số để thực hiện các chức năng của bộ nạp khởi động

- CPLD được sử dụng để tải dữ liệu cấu hình của một mảng cổng có thể lập trình trường từ bộ nhớ không bay hơi.

- Nói chung, chúng được sử dụng trong các ứng dụng thiết kế nhỏ như giải mã địa chỉ

- CPLD thường được sử dụng trong nhiều ứng dụng như trong các thiết bị di động chạy bằng pin, nhạy cảm về chi phí do kích thước nhỏ và sử dụng ít năng lượng.

Do đó, đây là tất cả về kiến trúc thiết bị logic có thể lập trình phức tạp và các ứng dụng của nó. Chúng tôi hy vọng rằng bạn đã hiểu rõ hơn về khái niệm này. Hơn nữa, bất kỳ truy vấn nào liên quan đến khái niệm này hoặc để thực hiện bất kỳ dự án điện và điện tử nào , hãy đóng góp ý kiến quý báu của bạn bằng cách bình luận trong phần bình luận bên dưới. Đây là một câu hỏi cho bạn, sự khác biệt giữa CPLD và FPGA là gì?

Tín ảnh:

- CPLD wikimedia

- Kiến trúc của CPLD slidesharecdn