Các Hiển thị bảy đoạn được sử dụng thường xuyên nhất là màn hình kỹ thuật số trong máy tính, máy đếm kỹ thuật số, đồng hồ kỹ thuật số, dụng cụ đo lường, v.v. Thông thường, các màn hình như LED cũng như LCD được sử dụng để hiển thị các ký tự cũng như số. Tuy nhiên, màn hình bảy phân đoạn được sử dụng để hiển thị cả số và ký tự. Các màn hình này thường được điều khiển bởi các giai đoạn đầu ra của kỹ thuật số mạch tích hợp như bộ đếm thập kỷ cũng như các chốt. Tuy nhiên, kết quả đầu ra của chúng thuộc loại 4-bit BCD (Số thập phân được mã hóa nhị phân) , do đó không thích hợp để vận hành trực tiếp màn hình bảy phân đoạn. Vì vậy, một bộ giải mã hiển thị có thể được sử dụng để chuyển đổi mã BCD thành mã bảy đoạn. Nói chung, nó có bốn dòng đầu vào cũng như bảy dòng đầu ra. Bài viết này thảo luận về cách thiết kế một màn hình BCD thành bảy đoạn mạch giải mã sử dụng cổng logic.

Lý thuyết bộ giải mã hiển thị BCD đến bảy đoạn

Các người giải mã là một thành phần thiết yếu trong Bộ giải mã BCD sang bảy đoạn . Bộ giải mã không là gì ngoài một mạch logic tổ hợp chủ yếu được sử dụng để chuyển đổi BCD sang một số thập phân tương đương. Nó có thể là một bộ giải mã BCD đến bảy đoạn. A mạch logic tổ hợp có thể được xây dựng với cổng logic trong đó bao gồm đầu vào cũng như đầu ra. Đầu ra của mạch này chủ yếu nằm ở điều kiện hiện tại của các đầu vào. Các ví dụ tốt nhất của mạch này là bộ ghép kênh , bộ phân kênh , bộ cộng, người trừ , bộ mã hóa, bộ giải mã, v.v.

BCD đến hiển thị bảy đoạn

Thiết kế mạch, cũng như hoạt động, chủ yếu phụ thuộc vào các khái niệm đại số Boolean cũng như các cổng logic. Một đoạn bảy Mạch hiển thị LED có thể được xây dựng với tám đèn LED. Các thiết bị đầu cuối chung là cực dương hoặc cực âm. Một màn hình hiển thị bảy đoạn cathode chung bao gồm 8 chân trong đó chân 7 là chân đầu vào được đánh dấu từ a đến g & chân thứ 8 là chân nối đất.

Thiết kế mạch giải mã hiển thị BCD sang 7 đoạn

Việc thiết kế Bộ giải mã hiển thị BCD sang bảy đoạn mạch chủ yếu bao gồm bốn bước cụ thể là phân tích, thiết kế bảng sự thật, Bản đồ K và thiết kế một mạch logic tổ hợp sử dụng các cổng logic.

Bước đầu tiên của thiết kế mạch này là phân tích màn hình hiển thị bảy đoạn catốt chung. Màn hình này có thể được cấu tạo với bảy đèn LED ở dạng H. Một bảng chân trị của mạch này có thể được thiết kế bởi các kết hợp đầu vào cho mọi chữ số thập phân. Ví dụ: số thập phân ‘1’ sẽ kiểm soát sự pha trộn của b & c.

Bước thứ hai là thiết kế bảng sự thật bằng cách liệt kê màn hình hiển thị tín hiệu đầu vào-7, số nhị phân tương đương gồm bốn chữ số cũng như số thập phân.

Việc thiết kế bảng chân trị cho bộ giải mã chủ yếu phụ thuộc vào loại màn hình. Chúng ta đã thảo luận ở trên rằng, đối với màn hình cathode thông thường, đầu ra bộ giải mã phải cao để nhấp nháy phân đoạn.

Dạng bảng của bộ giải mã BCD sang 7 đoạn với màn hình cực âm chung được hiển thị bên dưới. Bảng sự thật bao gồm bảy cột o / p tương đương với mỗi cột trong số bảy phân đoạn. Ví dụ, cột cho một đoạn minh họa các cách sắp xếp khác nhau mà nó sẽ sáng lên. Do đó, phân đoạn ‘a’- là năng lượng cho các chữ số như 0, 2, 3, 5, 6, 7, 8 & 9.

Chữ số | X | Y | VỚI | TRONG | đến | b | c | d | Là | f | g |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| hai | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

3 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 4 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

5 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 6 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

7 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| số 8 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 9 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

Bằng cách sử dụng bảng sự thật ở trên, đối với mọi hàm đầu ra, biểu thức Boolean có thể được viết.

a = F1 (X, Y, Z, W) = ∑m (0, 2, 3, 5, 7, 8, 9)

b = F2 (X, Y, Z, W) = ∑m (0, 1, 2, 3, 4, 7, 8, 9)

c = F3 (X, Y, Z, W) = ∑m (0, 1, 3, 4, 5, 6, 7, 8, 9)

d = F4 (X, Y, Z, W) = ∑m (0, 2, 3, 5, 6, 8)

e = F5 (X, Y, Z, W) = ∑m (0, 2, 6, 8)

f = F6 (X, Y, Z, W) = ∑m (0, 4, 5, 6, 8, 9)

g = F7 (X, Y, Z, W) = ∑m (2, 3, 4, 5, 6, 8, 9)

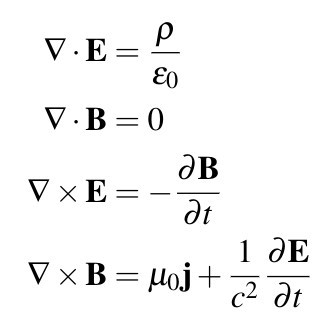

Bước thứ ba trong thiết kế này chủ yếu liên quan đến việc thiết kế K-map (Bản đồ của Karnaugh) cho mọi biểu thức đầu ra cũng như sau đó rút ngắn chúng để có được tổ hợp logic đầu vào cho mọi đầu ra.

Đơn giản hóa Karnaugh -Map

Việc đơn giản hóa bản đồ k của bộ giải mã 7 đoạn catốt chung có thể được thực hiện để lập kế hoạch cho mạch tổ hợp. Từ sự đơn giản hóa K-map ở trên, chúng ta có thể nhận được các phương trình đầu ra như sau

a = X + Z + YW + Y'W '

b = Y ’+ Z’W’ + ZW

c = Y + Z '+ W

d = Y’W ’+ ZW’ + YZ’W + Y’Z + X

e = Y’W ’+ ZW’

f = X + Z’W ’+ YZ’ + YW ’

g = X + YZ ’+ Y’Z + ZW’

Bước cuối cùng của việc này là thiết kế một mạch logic sử dụng các phương trình ánh xạ k ở trên. Một mạch tổ hợp có thể được xây dựng bằng cách sử dụng 4 đầu vào là A, B, C, D và các đầu ra trên màn hình như a, b, c, d, e, f, g. Hoạt động của mạch logic trên có thể được hiểu chỉ với sự trợ giúp của bảng sự thật. Khi tất cả các i / ps được kết nối với logic nhỏ.

Mạch giải mã BCD sang Bảy đoạn

Sau đó, đầu ra của mạch logic tổ hợp sẽ điều khiển từng và mọi đèn LED đầu ra ngoài ‘g’ để truyền. Do đó số ‘0’ sẽ được trưng bày. Tương tự, đối với tất cả các nhóm khác của các công tắc đầu vào, quá trình tương tự sẽ diễn ra.

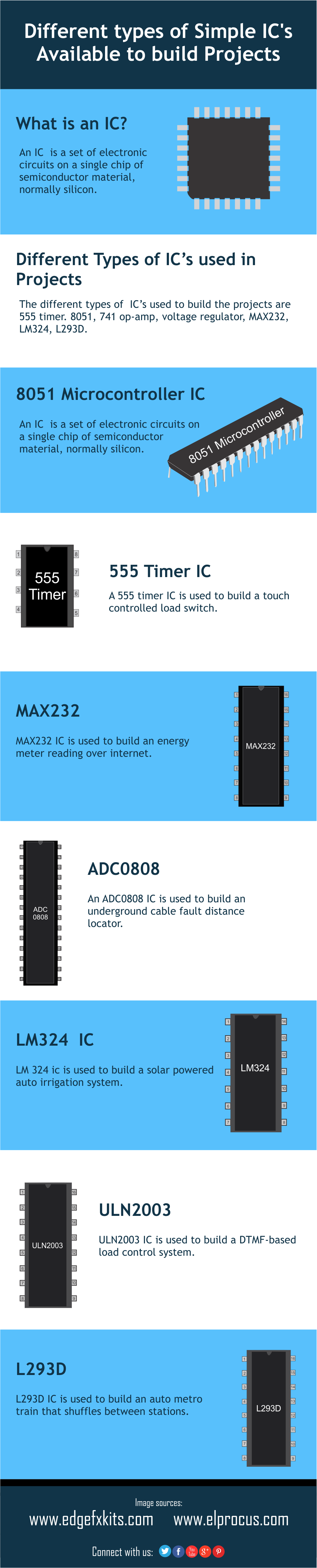

BCD Bảy đoạn hiển thị sử dụng IC 7447

Về cơ bản, điốt phát quang có hai loại 'là cực âm chung CC và cực dương chung CA. Ở cực âm thông thường, tất cả 8 đầu cực dương chỉ sử dụng một đầu cực âm cực duy nhất, điều này quen thuộc. Trong khi ở cực dương chung, đầu cuối quen thuộc của tất cả cực âm là loại cực dương.

BCD bảy đoạn hiển thị sử dụng IC7447

Bộ giải mã là một loại mạch logic tổ hợp kết nối dữ liệu nhị phân từ n dòng đầu vào đến 2n dòng đầu ra. Các IC7447 IC là một bộ giải mã BCD sang bảy đoạn. IC7447 này có Số thập phân được mã nhị phân giống như đầu vào cũng như đưa ra các đầu ra như mã bảy đoạn có liên quan.

Vì vậy, đây là tất cả về màn hình bộ giải mã BCD sang 7 đoạn. Từ thông tin trên, cuối cùng, chúng ta có thể kết luận rằng mạch này có thể thay đổi được với các bộ định thời cũng như bộ đếm để hiển thị các xung CLK, và cũng được sử dụng như một mạch hẹn giờ. Đây là một câu hỏi dành cho bạn, Karnaugh -Map là gì?