Trong hầu hết các mạch sạc pin tự động trong blog này, bạn có thể đã thấy một opamp có tính năng trễ bao gồm cho một số chức năng quan trọng. Bài viết sau giải thích ý nghĩa và kỹ thuật thiết kế cho chức năng trễ trong mạch opamp.

Để tìm hiểu chính xác hiện tượng trễ kinh bạn có thể tham khảo bài viết này giải thích độ trễ thông qua một ví dụ về rơ le

Nguyên lý hoạt động

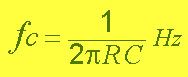

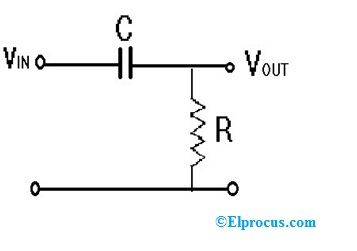

Hình 2 thể hiện thiết kế thông thường cho bộ so sánh mà không sử dụng độ trễ. Sự sắp xếp này hoạt động bằng cách sử dụng bộ chia điện áp (Rx và Ry) để thiết lập điện áp ngưỡng tối thiểu.

Bộ so sánh sẽ đánh giá và so sánh tín hiệu đầu vào hoặc điện áp (Vln) với điện áp ngưỡng đặt (Vth).

Điện áp nguồn cấp đầu vào của bộ so sánh sẽ được so sánh được kết nối với đầu vào đảo ngược, kết quả là đầu ra sẽ có phân cực ngược.

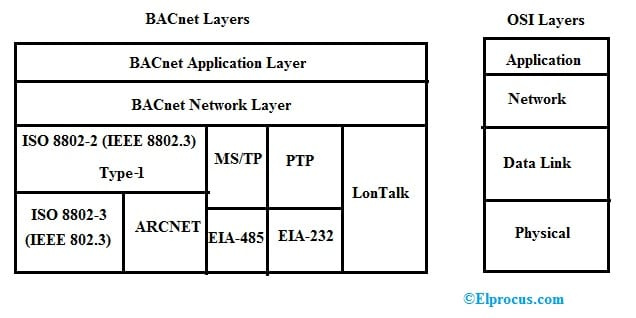

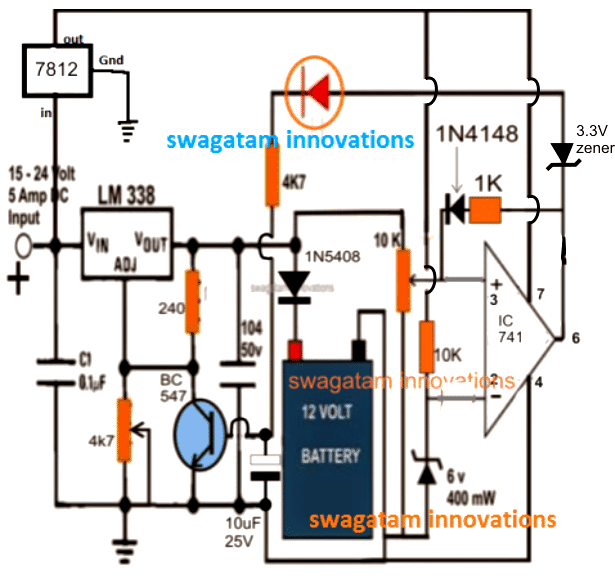

Mỗi lần Vin> Vth, đầu ra được cho là gần với nguồn cung cấp âm (GND hoặc mức logic thấp cho sơ đồ được hiển thị). và khi Vln Giải pháp dễ dàng này cho phép bạn quyết định xem tín hiệu chính hãng, ví dụ như nhiệt độ có nằm trên một giới hạn ngưỡng quyết định nhất định hay không. Mặc dù vậy, sử dụng kỹ thuật này có thể gặp phải tình trạng khó khăn. Sự can thiệp vào tín hiệu nguồn cấp dữ liệu đầu vào có thể khiến đầu vào thay đổi trên và dưới ngưỡng đã đặt, dẫn đến kết quả đầu ra không nhất quán hoặc dao động. Hình 3 minh họa đáp ứng đầu ra của bộ so sánh không có độ trễ với mẫu điện áp đầu vào dao động. Trong khi điện áp tín hiệu đầu vào đạt đến giới hạn cài đặt (bởi mạng phân áp) (Vth = 2,5V), nó sẽ điều chỉnh trên cũng như dưới ngưỡng tối thiểu trong một số trường hợp. Kết quả là đầu ra dao động quá phù hợp với đầu vào. Trong các mạch thực tế, đầu ra không ổn định này có thể dễ dàng gây ra các vấn đề bất lợi. Như một minh họa, hãy nghĩ về tín hiệu đầu vào là một tham số nhiệt độ và phản hồi đầu ra là một ứng dụng quan trọng dựa trên nhiệt độ, điều này sẽ được giải thích bởi một bộ vi điều khiển. Đáp ứng tín hiệu đầu ra dao động có thể không đóng góp thông tin trung thực cho bộ vi điều khiển và có thể tạo ra các kết quả 'khó hiểu' cho bộ vi điều khiển ở các mức ngưỡng quan trọng. Ngoài ra, hãy tưởng tượng rằng đầu ra của bộ so sánh được yêu cầu để vận hành một động cơ hoặc van. Việc chuyển đổi không nhất quán này trong các giới hạn ngưỡng có thể buộc van hoặc động cơ được BẬT / TẮT nhiều lần trong các tình huống ngưỡng quan trọng .. Nhưng một giải pháp 'mát mẻ' thông qua một sự thay đổi nhỏ đối với mạch so sánh cho phép bạn bao gồm độ trễ, từ đó loại bỏ hoàn toàn đầu ra chập chờn trong quá trình thay đổi ngưỡng. Độ trễ tận dụng một số giới hạn điện áp ngưỡng riêng biệt để giữ rõ ràng khỏi các chuyển đổi dao động như đã thấy trong mạch đã thảo luận. Nguồn cấp tín hiệu đầu vào cần phải vượt qua ngưỡng trên (VH) để tạo ra sự thay đổi của đầu ra thấp hoặc dưới giới hạn ngưỡng đặt dưới (VL) để chuyển sang đầu ra cao. Hình 4 chỉ ra độ trễ trên bộ so sánh. Điện trở Rh khóa ở mức ngưỡng trễ. Mỗi khi đầu ra ở mức logic cao (5V), Rh vẫn song song với Rx. Điều này đẩy thêm dòng điện vào Ry, nâng điện áp giới hạn ngưỡng (VH) lên 2,7V. Tín hiệu đầu vào có thể sẽ cần phải vượt lên trên VH = 2.7V để thúc đẩy phản ứng đầu ra di chuyển xuống mức logic thấp (0V). Trong khi đầu ra ở mức logic thấp (0V), Rh được đặt song song với Ry. Điều này làm giảm dòng điện vào Ry, làm giảm điện áp ngưỡng xuống còn 2,3V. Tín hiệu đầu vào sẽ muốn xuống dưới VL = 2.3V để giải quyết đầu ra lên mức logic cao (5V). Hình 5 biểu thị đầu ra của bộ so sánh có độ trễ với điện áp đầu vào dao động. Mức tín hiệu đầu vào được cho là vượt qua giới hạn ngưỡng cao hơn (VH = 2.7V) để đầu ra opamp trượt xuống mức logic thấp (0V). Ngoài ra, mức tín hiệu đầu vào cần phải di chuyển dưới ngưỡng Dưới để đầu ra opamp có thể leo lên mức logic cao (5V) một cách suôn sẻ. Sự nhiễu loạn trong ví dụ này có thể không đáng kể và do đó có thể được bỏ qua, nhờ vào độ trễ. Nhưng đã nói điều này, trong trường hợp mức tín hiệu đầu vào cao hơn phạm vi tính toán độ trễ (2.7V - 2.3V) có thể dẫn đến việc tạo ra các phản ứng chuyển đổi đầu ra dao động bổ sung. Để khắc phục điều này, thiết lập phạm vi độ trễ cần được mở rộng đủ để loại bỏ nhiễu cảm ứng trong mô hình mạch cụ thể đã cho. Phần 2.1 cung cấp cho bạn một giải pháp để xác định các thành phần để sửa các ngưỡng phù hợp với nhu cầu ứng dụng đã chọn của bạn. Phương trình (1) và (2) có thể giúp ích để quyết định các điện trở muốn tạo ra các điện áp ngưỡng trễ VH và VL. Một giá trị duy nhất (RX) được yêu cầu để được chọn tùy ý. Trong hình minh họa này, RX đã xác định 100k để giúp giảm tỷ lệ hòa hiện tại. Rh được tính là 575k, theo đó giá trị tiêu chuẩn tức thì 576k đã được thực hiện. Xác nhận cho các phương trình (1) và (2) được trình bày trong Phụ lục A. Rh / Rx = VL / VH - VL Chúng tôi lấy ví dụ về mạch sạc pin IC 741 và tìm hiểu cách điện trở trễ phản hồi cho phép người dùng đặt ngắt sạc đầy và khôi phục sạc thấp của rơ le cách nhau bởi một số chênh lệch điện áp. Nếu độ trễ không được đưa vào, rơ le sẽ nhanh chóng BẬT TẮT ở mức cắt gây ra sự cố nghiêm trọng với hệ thống. Câu hỏi được đưa ra bởi một trong những độc giả tận tâm của blog này, ông Mike. Câu hỏi: 1) Hi mạch này rất thiên tài! Nhưng tôi có một số câu hỏi về opamps so sánh Tại sao 4,7 zombies được sử dụng cho điện áp tham chiếu? Nếu chúng ta không muốn 12 volt giảm xuống dưới 11 để phóng điện, tại sao giá trị zener thấp như vậy? Điện trở nguồn cấp trở lại điểm nối đất ảo có phải là điện trở 100K không? Nếu vậy, tại sao giá trị này được chọn? Cảm ơn vì bất kì sự giúp đỡ! 2) Ngoài ra, tôi xin lỗi, tôi đã quên là tại sao lại có 4,7 zen ở chân đế của các bóng bán dẫn BC 547? 3) Cũng là câu hỏi cuối cùng của tôi cho ngày hôm nay cho mạch này. Đèn LED chỉ báo màu đỏ / xanh lục làm thế nào để chúng sáng lên? Ý tôi là đèn LED màu đỏ được kết nối thông qua điện trở của nó với đầu + thanh ray, kết nối với đầu ra của OPAMP, sau đó đi xuống theo chuỗi về phía đèn LED màu xanh lá cây. Có vẻ như chúng sẽ bật cả hai cùng một lúc, vì chúng mắc nối tiếp, trong cả hai mạch. Nó có liên quan gì đến mạch phản hồi và nối đất ảo không? Ồ, tôi nghĩ tôi có thể thấy. Vì vậy, khi OPAMP tắt, đèn LED màu đỏ trên cùng Dòng điện đang đi qua điện trở phản hồi (do đó 'bật' của nó) đến điểm đất ảo? Nhưng làm thế nào để nó tắt, khi OPAMP có đầu ra? Khi OP AMP nhận được một đầu ra, tôi có thể thấy nó đi xuống đèn LED màu xanh lá cây, nhưng làm thế nào, ở trạng thái đó, đèn LED màu đỏ sau đó bị tắt? Cám ơn lần nữa cho bất kì sự giúp đỡ nào! Phản hồi của tôi 4,7 không phải là một giá trị cố định, nó cũng có thể được thay đổi thành các giá trị khác, giá trị đặt trước chân số 3 cuối cùng sẽ điều chỉnh và hiệu chỉnh ngưỡng theo giá trị zener selecte. Câu hỏi Vì vậy, điện áp tham chiếu là zener ở chân 2 (opamp xem trên) đúng không? Điện trở phản hồi 100K và nồi đang tạo ra giá trị độ trễ (nghĩa là, sự khác biệt giữa chân 2 và 3 để làm cho opamp xoay cao với điện áp + đường sắt của nó)? OpAmp trong cấu hình này luôn cố gắng làm cho chân 2 và 3 đến cùng một giá trị thông qua điện trở phản hồi của nó, chính xác (không, vì bộ chia phản hồi là @ 0 và chân 3 là @ đất)? Tôi đã thấy bộ điều khiển bộ sạc năng lượng mặt trời này được thực hiện mà không cần nguồn cấp lại, chỉ sử dụng một số opamps với các chân tham chiếu điện áp và một cái nồi trên cái kia. Tôi chỉ đang cố gắng hiểu độ trễ hoạt động như thế nào trong trường hợp này, tôi không hiểu toán học trong mạch này. Phản hồi đặt trước 100k 10k có thực sự cần thiết không? Trong các mạch opamp khác, chúng không sử dụng bất kỳ nguồn cấp dữ liệu nào mà chỉ sử dụng chúng ở chế độ cấu hình so sánh với điện áp ref ở chân đảo ngược / không đảo ngược và khi vượt quá một mức, opamp sẽ chuyển sang điện áp đường ray của nó Nguồn cấp dữ liệu trở lại đang làm gì? Tôi hiểu công thức khuếch đại opamp, trong trường hợp này có phải là chênh lệch điện áp 100k / 10k x của giá trị điện áp POT (đặt trước) và 4,7 zener không? Hay đây là kiểu kích hoạt Schmidt của mạch UTP LTP trễ Tôi vẫn không nhận được nguồn cấp dữ liệu trở lại với 100k / 10k bộ so sánh opamp hầu hết mà tôi đã thấy chỉ sử dụng opamp trong bão hòa, bạn có thể giải thích tại sao phản hồi và đạt được cho điều này không? Được rồi, tôi không hiểu giá trị đặt trước 10K được sử dụng để phân chia điện áp từ thanh ray 12volt, đúng không? Vì vậy, khi giá trị đặt trước của nó theo POT gạt nước nhiều hơn? hơn zener 4,7V, chúng tôi xoay opamp cao? vẫn không nhận được phản hồi 100k và tại sao nó được sử dụng trong mạch so sánh Phản hồi của tôi Vui lòng tham khảo hình ví dụ trên để hiểu cách hoạt động của điện trở phản hồi trong mạch Opamp Tôi chắc rằng bạn biết về cách hoạt động của bộ chia điện áp? Ngay khi đầy đủ ngưỡng sạc được phát hiện, theo sự điều chỉnh của chân số 3 đặt trước, điện áp ở chân số 3 chỉ cao hơn điện áp zener chân số 2, điều này buộc đầu ra opamp phải chuyển sang mức cung cấp từ 0 volt trước đó của nó .... nghĩa là nó thay đổi từ 0 đến 14V ngay lập tức. Trong tình huống này, bây giờ chúng ta có thể giả định rằng phản hồi được kết nối giữa 'nguồn cung cấp tích cực' và chân số 3 ... khi điều này xảy ra, điện trở phản hồi bắt đầu cung cấp 14V này cho chân số 3, có nghĩa là nó củng cố thêm điện áp đặt trước và thêm một số thêm vôn tùy thuộc vào giá trị điện trở của nó, về mặt kỹ thuật, điều này có nghĩa là phản hồi này trở nên song song với điện trở đặt trước được đặt giữa nhánh giữa và nhánh dương. Vì vậy, giả sử trong quá trình chuyển đổi chân số 3 là 4,8V và điều này đã chuyển đầu ra thành mức nguồn cung cấp và cho phép nguồn cung cấp tiếp cận trở lại chân số 3 thông qua điện trở phản hồi, điều này làm cho chân số 3 cao hơn một chút ở mức 5V .... do chân số 3 này điện áp sẽ mất nhiều thời gian hơn để trở lại dưới mức giá trị zener 4.7V vì nó đã được nâng lên 5V ... điều này được gọi là độ trễ. Cả hai đèn LED sẽ không bao giờ sáng bởi vì đường giao nhau của chúng được kết nối với chân số 6 của opamp sẽ ở mức 0V hoặc điện áp cung cấp sẽ đảm bảo rằng đèn LED màu đỏ sáng lên hoặc màu xanh lá cây, nhưng không bao giờ cùng nhau. Câu hỏi Cảm ơn bạn đã trả lời tất cả các câu hỏi của tôi, đặc biệt là câu hỏi về phản hồi, có vẻ như cấu hình hơi nâng cao vì vậy nó mới đối với tôi nếu tùy chọn mạch điểm đặt điện áp thấp này hoạt động cũng như 14 volt trên không đảo ngược, 12 volt zener trên đảo ngược chân tham chiếu. Khi đường ray 14 VDC giảm xuống còn 12, đầu ra opamp sẽ bật. Điều này sẽ kích hoạt phần điện áp thấp của mạch. Trong trường hợp của bạn, nồi 10k chỉ là 'điều chỉnh', 'phân chia' hoặc đưa đường ray 14volt đến điện áp gần hơn với 4.7zener? Bạn vẫn điều khiển 14 VDC. Ý tôi là một khi nó lên đến 11 VDC, v.v., bạn muốn một tỷ lệ sẽ tăng opamp cao. Nếu bạn thay thế giá trị 4,7 bằng một giá trị zener khác, bộ chia nồi sẽ thiết lập một tỷ lệ mới, nhưng nồi vẫn 'theo' hoặc tỷ lệ với thanh ray 14 VDC? Thay vì đặt 14VDC trên một chân opamp, bạn thả nó qua một bộ chia, nhưng tỷ lệ vẫn kiểm soát một mức giảm nhỏ từ 14VDC xuống 11 VDC qua nồi 10K, điều đó sẽ giảm xuống 4,7V? Tôi chỉ đang cố gắng hiểu cách mạch đóng 'lan truyền' từ 11VDC (nơi chúng tôi muốn điểm đặt điện áp thấp) và điện áp ref là 4,7 vdc. hầu hết các mạch so sánh mà tôi đã thấy chỉ có vdc ref ở chân 2, ví dụ 6 VDC. và điện áp đường sắt nói rằng 12 VDC. Sau đó, một cái nồi thiết lập một bộ chia từ thanh ray 12VDC đó, giảm xuống còn 6 VDC thông qua điểm giữa của bộ chia. Khi điện áp ở chân 3 tiếp cận với ref 6 VDC @ chân 2, opamp sẽ thay đổi theo cấu hình của nó, (đảo ngược hoặc không đảo ngược) Có lẽ nơi tôi đang làm rối là ở đây- trong các mạch khác mà tôi đã xem xét, điện áp đường sắt được cho là cứng, nhưng trong trường hợp này, nó sẽ giảm Sự sụt giảm đó (14VDC xuống 11VDC) làm rối loạn bộ chia điện áp 10K tỉ lệ? Và bạn sử dụng tỷ lệ đó để tham chiếu zener 4,7? vì vậy nếu bạn có bình 10K ở vị trí giữa của nó là 5 k, bộ chia đó sẽ đặt 14VDC ở 7 VDC (R2 / R1 + R2) nếu thanh 14 đi đến 11 VDC, vị trí giữa của bộ chia bây giờ là 5,5, vì vậy nó phụ thuộc vào vị trí cần gạt nước, tôi có bắt đầu lấy nó không? Chúng tôi chỉ cần điều chỉnh gạt nước cho đến khi tỷ lệ 4,7 với bộ chia điện áp và đường ray giảm chúng tôi muốn? vì vậy mạch này đang sử dụng các nguyên tắc so sánh opamp thông thường, nhưng với ảnh hưởng thêm của hystersis cho điều khiển điểm đặt điện áp thấp? Phản hồi của tôi Có bạn đang làm đúng. Một zener 12V cũng sẽ hoạt động, nhưng điều đó sẽ khiến opamp chuyển đổi giữa 12V và 12,2V, hệ thống feedaback cho phép opamp chuyển đổi giữa 11V và 14V, đó là lợi thế chính của việc sử dụng điện trở trễ phản hồi. Tương tự trong trường hợp của tôi, nếu điện trở phản hồi bị loại bỏ, opamp sẽ bắt đầu dao động thường xuyên giữa mức cắt 14,4V và mức hoàn nguyên 14,2V. bởi vì theo cài đặt của cài đặt trước 10K, opamp sẽ cắt ở 14,4V và ngay sau khi điện áp pin giảm xuống một vài mili-volt, opamp sẽ lại TẮT và điều này sẽ tiếp tục gây ra BẬT / TẮT liên tục chuyển mạch của rơ le. Tuy nhiên, tình huống trên sẽ ổn nếu không sử dụng rơ le thay vì sử dụng bóng bán dẫn. Câu hỏi Thông thường những gì tôi thấy trong các bộ so sánh là một điện áp cố định như bạn có @ chân 2, thường thông qua bộ chia điện áp hoặc zener, v.v., sau đó ở chân 3 một điện áp thay đổi từ cấu hình nguồn - nồi - đất với gạt nước (nồi) ở giữa và gạt nước sẽ tìm điểm đặt của chốt 2. Trong trường hợp của bạn điện áp zener 4,7 cố định và xoay opamp khoảng với đường ray của nó, theo cấu hình của nó, nơi khó hiểu là cần gạt nước 10K trong mạch của bạn được đặt ở 14,4 volt? Sau đó, điều đó được cho là chuyến đi của zener 4,7? Tôi không nhận được trận đấu? Phản hồi của tôi đầu tiên chúng tôi đặt ngưỡng trên cắt qua nồi bằng cách cung cấp 14,4V từ nguồn điện biến đổi với điện trở phản hồi bị ngắt kết nối. sau khi thiết lập ở trên, chúng tôi kết nối một điện trở trễ được chọn chính xác trong khe cắm, và sau đó bắt đầu giảm điện áp cho đến khi chúng tôi tìm thấy opamp tắt ở mức thấp hơn mong muốn nói 11V. điều này thiết lập mạch hoàn hảo. NGAY BÂY GIỜ, trước khi xác nhận điều này trên thực tế, chúng tôi đảm bảo rằng pin được kết nối lần đầu tiên và sau đó nguồn được BẬT. điều này rất quan trọng để nguồn điện có thể được kéo xuống theo mức pin và bắt đầu với mức chính xác bằng mức xả pin. đó là tất cả, sau đó tất cả đều suôn sẻ với opamp theo mô hình cắt bỏ như người dùng đã thiết lập. Một điều quan trọng khác là dòng điện cung cấp phải ở khoảng 1/10 AH của pin để nguồn điện có thể dễ dàng kéo xuống theo mức pin ban đầu. Câu hỏi Vâng, tôi đã suy nghĩ kỹ và nếu không có hiện tượng trễ thì nó sẽ không hoạt động. Nếu tôi đặt một zener 7 ở chân 2, đặt Vin @ pin 3 thông qua một bộ chia điện áp 5k là 7 vôn, và một pin đã xả trên mạch, ngay sau khi pin được sạc đến 14 vôn, rơ le sẽ rơi vào và kéo tải vào, nhưng tải sẽ tụt số 7 ở nồi xuống ngay lập tức nên rơle sẽ rớt ra. Nếu không có hiện tượng trễ, bây giờ tôi có thể hiểu tại sao tôi không làm việc, cảm ơn Phản hồi của tôi Ngay cả khi không có tải, pin sẽ không bao giờ bám vào giới hạn 14,4V và sẽ ngay lập tức cố gắng ổn định xuống khoảng 12,9V hoặc 13V. Khi opamp o / p chuyển sang (+), nó trở nên tốt như đường ray cung cấp, có nghĩa là điện trở phản hồi được liên kết với đường ray cung cấp, điều đó ngụ ý thêm rằng chân số 3 phải chịu một điện áp song song riêng biệt ngoài đặt trước điện trở phần trên được kết nối với đường ray cung cấp. Điện áp bổ sung này từ phản hồi làm cho chân # 3 tăng từ 4,7V để nói là 5V ... điều này thay đổi tính toán cho chân3 / 2 và buộc opamp phải giữ chốt cho đến khi 5V giảm xuống dưới 4,7v, điều này chỉ xảy ra khi điện áp pin giảm xuống 11V .... nếu không có điều này, opamp sẽ phải chuyển đổi liên tục giữa 14,4V và 14,2V Cuộc thảo luận sau đây cho chúng ta biết liên quan đến điện áp sạc đầy cho pin axit chì là gì và ý nghĩa của độ trễ trong hệ thống sạc pin. Các câu hỏi được đặt ra bởi ông Girish Thảo luận về các thông số sạc pin Hoàn toàn phí cắt và độ trễ Theo quy luật chung, dòng điện này có thể vào khoảng Ah / 70, tức là nhỏ hơn từ 50 đến 100 lần so với định mức AH của pin. Ví dụ: nếu một opamp không có tính năng trễ được định cấu hình để theo dõi tình trạng sạc quá mức trong hệ thống sạc pin, thì ở mức sạc đầy ngay sau khi nó cắt nguồn sạc cho pin, pin sẽ có xu hướng sụt giảm. điện áp và cố gắng giải quyết xuống một số vị trí điện áp thấp hơn. Bạn có thể so sánh nó với việc bơm không khí vào bên trong ống, miễn là áp suất bơm còn không khí bên trong ống giữ được, nhưng ngay khi ngừng bơm, ống bắt đầu xì hơi từ từ… điều tương tự cũng xảy ra với pin. Khi điều này xảy ra, tham chiếu đầu vào opamp sẽ hoàn nguyên và đầu ra của nó được nhắc BẬT sạc lại, điều này lại đẩy điện áp pin về ngưỡng cắt cao hơn và chu kỳ tiếp tục lặp lại ……. hành động này tạo ra sự chuyển đổi nhanh chóng đầu ra opamp ở ngưỡng sạc đầy. Điều kiện này thường không được khuyến nghị trong bất kỳ hệ thống so sánh được điều khiển bằng opamp nào và điều này có thể làm phát sinh tiếng ồn chuyển tiếp. Để ngăn chặn điều này, chúng tôi thêm một điện trở trễ qua chân đầu ra và chân cảm biến của opamp, để ở giới hạn cắt, opamp sẽ tắt đầu ra và chốt ở vị trí đó, trừ khi và cho đến khi đầu vào nguồn cấp cảm biến đã thực sự giảm xuống giới hạn dưới không an toàn (trong đó độ trễ oamp không thể giữ chốt), opamp sau đó lại BẬT. Nếu bạn có thêm nghi ngờ liên quan đến điện áp sạc đầy cho pin axit chì và ý nghĩa độ trễ trong hệ thống sạc pin, đừng ngần ngại đưa ra thông qua các bình luận.Bộ so sánh không có độ trễ

Bộ so sánh với độ trễ

Đầu ra Compartaor với đầu vào dao động

Thiết kế bộ so sánh độ trễ

Thảo luận về hiện tượng trễ với một ví dụ thực tế

Tại sao tham chiếu Zener được sử dụng

Tại sao điện trở phản hồi được sử dụng

Trễ là gì

Cách thiết lập Ngưỡng chuyến đi

Điện áp sạc đầy và độ trễ là gì

Tôi có một vài câu hỏi khiến tôi vò đầu bứt tai:

1) Điện áp đầy của pin đối với pin Axit-Chì tiêu chuẩn là bao nhiêu, ở điện áp pin cần phải cắt khỏi bộ sạc. Điện áp sạc nổi đối với pin axit chì phải là bao nhiêu.

2) Điện trở từ trễ là rất quan trọng trong mạch so sánh? không có nó nó sẽ hoạt động bình thường? Tôi đã truy cập và tìm thấy nhiều câu trả lời khó hiểu. Mong các bạn giải đáp. Các dự án đang được triển khai.

Trân trọng.

Xin chào Girish,

1) Đối với pin axit chì 12V, mức sạc đầy từ nguồn điện là 14,3V (giới hạn cắt), phí nổi có thể là lượng dòng điện thấp nhất ở điện áp này, ngăn pin tự phóng điện và cũng ngăn pin do sạc quá mức.

Độ trễ được yêu cầu trong opamp để ngăn chúng tạo ra đầu ra dao động (BẬT / TẮT) để đáp ứng với đầu vào dao động đang được giám sát bởi opamp.

Trước: Mạch điều khiển bơm phản lực một pha Tiếp theo: Cách tạo mạch kiểm tra độ ẩm của đất bằng một IC đơn 741