Thuật ngữ VLSI là viết tắt của “Công nghệ tích hợp quy mô rất lớn” liên quan đến việc thiết kế các mạch tích hợp (IC) bằng cách kết hợp hàng nghìn Linh kiện bán dẫn một cách logic thành một con chip duy nhất bằng cách các mạch logic khác nhau . Các IC này cuối cùng làm giảm không gian mạch bị chiếm dụng khi so sánh với các mạch có IC thông thường. Sức mạnh tính toán và sử dụng không gian là những thách thức chính của thiết kế VLSI. Thực hiện các dự án VLSI mở ra một sự nghiệp đầy thách thức và tươi sáng cho sinh viên cũng như các nhà nghiên cứu. Một số lĩnh vực xu hướng mới của VLSI là Mảng cổng lập trình trường ứng dụng (FPGA), thiết kế ASIC và SOC. Dưới đây là danh sách một số dự án VLSI dành cho những sinh viên đang tha thiết tìm kiếm các dự án trong lĩnh vực này. Bài viết này thảo luận tổng quan về các dự án VLSI dựa trên FPGA, Xilinx, IEEE, Mini, Matlab, v.v. được liệt kê bên dưới. Những dự án này rất hữu ích cho sinh viên kỹ thuật, sinh viên M.tech.

Dự án VLSI cho sinh viên kỹ thuật

Các dự án VLSI với phần tóm tắt dành cho sinh viên kỹ thuật điện tử được thảo luận dưới đây.

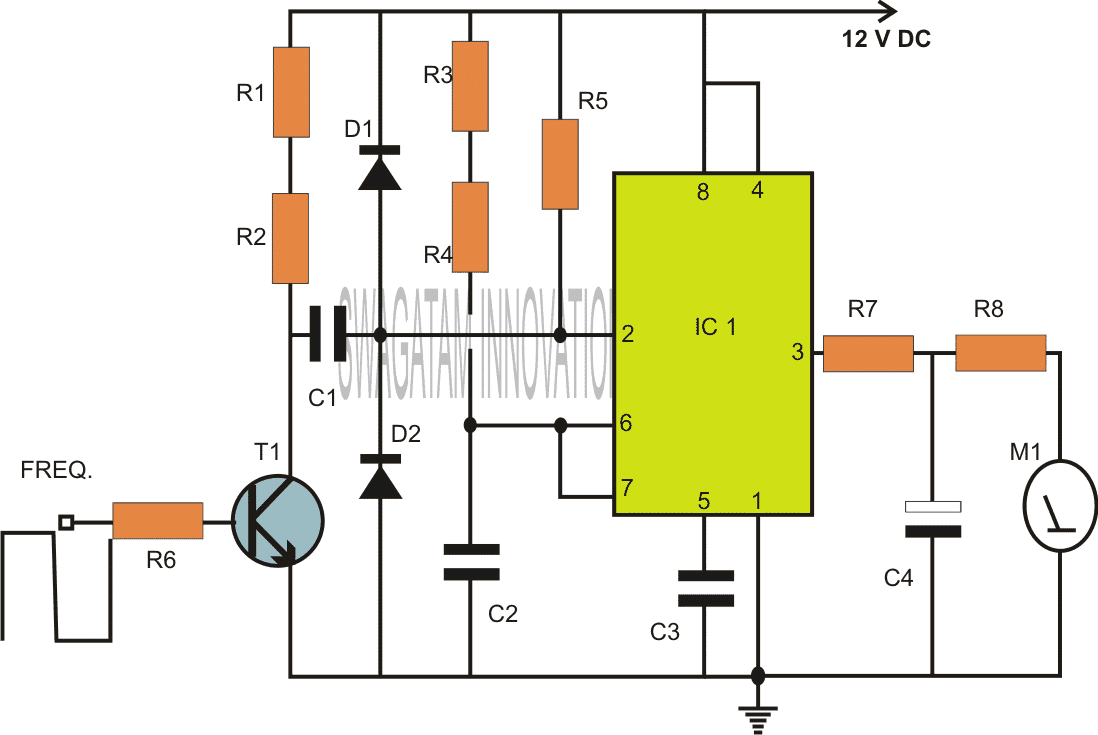

Dự án VLSI

1). Chuyển đổi Wavelet rời rạc dựa trên 3D Lifting

Dự án này giúp cung cấp hình ảnh có độ chính xác cao bằng cách sử dụng mã hóa hình ảnh mà không làm mất dữ liệu của nó. Để đạt được điều này, quá trình này thực hiện một bộ lọc nâng phụ thuộc vào sự biến đổi của kiến trúc VLSI wavelet rời rạc 3D.

2). Thiết kế Hệ nhân SFQ với 4 bit hiệu quả thông qua phần cứng tốc độ cao

Dự án này chủ yếu được sử dụng để triển khai bộ mã hóa gian hàng đã sửa đổi (MBE) với 4-bit SFQ dựa trên số nhân . Hệ số này cung cấp hiệu suất tốt khi so sánh với bộ mã hóa gian hàng thông thường. Dự án này chủ yếu được sử dụng trong các ứng dụng của độ trễ nghiêm trọng.

3). Bộ xử lý mật mã được sử dụng trong Thẻ thông minh với Khu vực hiệu quả

Dự án này được sử dụng để triển khai ba thuật toán mật mã được hỗ trợ bởi cả khóa riêng và khóa công khai được sử dụng trong thẻ thông minh ứng dụng cung cấp dữ liệu và xác minh người dùng cực kỳ an toàn giao tiếp .

4). Bộ nhân tốc độ cao hoặc công suất thấp với phương pháp triệt tiêu công suất giả

Hệ thống được đề xuất này lọc bỏ các tín hiệu sai vô ích của các đơn vị số học để tránh việc truyền dữ liệu không cần thiết không ảnh hưởng đến kết quả tính toán cuối cùng. Hệ thống này sử dụng phương pháp SPST cho các số nhân để đạt được công suất thấp và truyền dữ liệu tốc độ cao.

5). Nén & giải nén thuật toán dữ liệu không mất dữ liệu

Dự án này chủ yếu được thực hiện cho kiến trúc phần cứng 2 giai đoạn tùy thuộc vào tính năng thuật toán PDLZW (Parallel Dictionary LZW) cũng như thuật toán kiểu Huffman thích ứng được sử dụng cho cả hai ứng dụng nén dữ liệu không mất dữ liệu và giải nén không mất dữ liệu.

6). Kiến trúc của bộ giải mã Turbo với độ phức tạp thấp cho WSN tiết kiệm năng lượng

Hệ thống được đề xuất được sử dụng để giảm tổng mức tiêu thụ năng lượng trong suốt quá trình truyền dữ liệu của WSN thông qua thuật toán phân tách LUT-Log-BCJR thành các hoạt động ACS (Add Compare Select) cơ bản.

7). Kiến trúc VLSI để loại bỏ nhiễu xung của hình ảnh một cách hiệu quả

Hệ thống được đề xuất này chủ yếu được sử dụng để nâng cao chất lượng hình ảnh một cách trực quan nhằm tránh nguy cơ bị hỏng do nhiễu xung để triển khai kiến trúc VLSI hiệu quả với sự trợ giúp của bộ lọc bảo vệ cạnh.

số 8). Kiến trúc của một bộ xử lý trong bộ nhớ được sử dụng để nén đa phương tiện

Hệ thống được đề xuất này cung cấp một kiến trúc phức tạp thấp để bộ xử lý trong bộ nhớ để hỗ trợ các ứng dụng đa phương tiện cụ thể là nén hình ảnh, video thông qua việc áp dụng rất nhiều lệnh đơn, nhiều khái niệm dữ liệu và từ hướng dẫn.

9). Kỹ thuật đồng bộ hóa thời gian với tốc độ ký hiệu cho hệ thống OFDM không dây có công suất thấp

Hệ thống được đề xuất này chủ yếu được sử dụng để cải thiện hoạt động của OFDM không dây (Phân chia tần số trực giao Ghép kênh ) hệ thống thông qua việc giảm sức mạnh của toàn bộ băng tần với sự trợ giúp của đồng hồ máy phát điện với bộ điều khiển thời gian lấy mẫu có thể điều chỉnh pha & động.

10). Triển khai hệ số nhân tốc độ cao và công suất thấp dựa trên bộ tích lũy với SPST Adder & Verilog

Dự án này được sử dụng để thiết kế MAC (bộ nhân và bộ tích lũy) công suất thấp và tốc độ cao thông qua việc chấp nhận phương pháp triệt tiêu công suất sai trên MBE (bộ mã hóa gian hàng đã sửa đổi). Bằng cách sử dụng thiết kế này, có thể tránh được sự tiêu tán điện của toàn bộ chuyển mạch.

11). Thiết kế & Triển khai Bộ xử lý Robot bằng cách Cho phép Chống va chạm với Công nghệ RFID

Hệ thống được đề xuất chủ yếu được sử dụng để thực hiện một bộ xử lý robot có khả năng chống va chạm để tránh va chạm vật lý của robot trong môi trường nhiều robot. Thuật toán này chủ yếu được thực hiện bằng công nghệ VHDL & RFID.

12). Thiết kế mạch logic với năng lượng hiệu quả bằng phương pháp đoạn nhiệt

Hệ thống này thể hiện thiết kế mạch logic hiệu quả bằng phương pháp đoạn nhiệt khi so sánh thông qua thiết kế CMOS thông thường với sự trợ giúp của các mạch sử dụng Cổng NAND & NOR . Bằng cách sử dụng phương pháp đoạn nhiệt, có thể giảm sự tiêu tán công suất trong mạng cũng như tái chế năng lượng tích trữ trong tụ điện tải.

3). Hệ thống mã hóa để nâng cao tốc độ tính toán của hệ thống

Mục tiêu chính của dự án này là tăng cường bảo mật truyền dữ liệu để cải thiện tốc độ tính toán bằng cách triển khai thuật toán AES sử dụng FPGA. Vì vậy, mô phỏng này, cũng như thiết kế toán học, có thể được thực hiện với sự trợ giúp của mã VHDL.

14). Khối IP của AHM hoặc Bus hiệu suất cao nâng cao

Dự án này chủ yếu được sử dụng để thiết kế một kiến trúc của Advanced Vi điều khiển Bus (AMB) bằng cách sử dụng AHBN (Advanced High-Performance Bus). Dự án này có thể được thiết kế với mã VHDL bằng cách thực hiện các khối như master & save.

15). Bộ thu phát RF đa chế độ dựa trên DSM với đa kênh

Hệ thống này chủ yếu được sử dụng để thiết kế kiến trúc máy phát và máy thu đa chế độ và đa kênh RF với bộ điều chế Delta-Sigma. Hệ thống được đề xuất này sử dụng một ngôn ngữ VHDL để thực hiện hai kiến trúc.

16). Bộ tập trung của Knockout Switch sử dụng Chế độ truyền không đồng bộ

Bằng cách sử dụng dự án này, một công tắc loại trực tiếp dựa trên chuyển giao không đồng bộ có thể được thiết kế với sự trợ giúp của các công cụ như VHS & VHDL. Công tắc loại trực tiếp này có thể được sử dụng trong các mạng gói mạch ảo cũng như các ứng dụng của gói dữ liệu.

17). Tổng hợp hành vi mạch không đồng bộ

Dự án này chủ yếu được sử dụng để cung cấp kỹ thuật tổng hợp hành vi được sử dụng cho mạch không đồng bộ. Cả hai mẫu như balsa & triển khai không đồng bộ đều là các yếu tố chính trong thiết kế.

18). Thiết kế AMBA sử dụng Bộ điều khiển bộ nhớ tuân thủ của AHB

Dự án này được sử dụng để thiết kế một MC (bộ điều khiển bộ nhớ) phụ thuộc vào AMBA (Kiến trúc Bus vi điều khiển nâng cao) để điều khiển bộ nhớ hệ thống sử dụng bộ nhớ chính như SRAM & ROM.

19). Thực hiện trình quảng cáo trên cây

Bộ cộng cây mang dựa trên thiết kế VLSI được gọi là bộ cộng hiệu suất tốt nhất so với các bộ cộng nhị phân thông thường. Các bộ bổ sung được thực hiện bởi dự án này là cây nối dài, đá kogge và đá kogge thưa thớt.

20). Thiết kế dựa trên CORDIC Xoay góc cố định

Khái niệm chính của hệ thống được đề xuất này là biến các vectơ bằng cách sử dụng các góc cố định. Những góc này cần thiết cho trò chơi, người máy, đang xử lý hình ảnh , v.v ... Bằng cách sử dụng dự án này, phép quay vectơ có thể đạt được bằng cách sử dụng các góc cụ thể do thiết kế của CORDIC (máy tính kỹ thuật số quay tọa độ).

21). Thiết kế bộ lọc FIR với số học phân tán của bảng tra cứu

Hệ thống đề xuất này chủ yếu nâng cao Bộ lọc FIR hiệu suất bằng cách thiết kế nó bằng cách sử dụng số học phân tán của bảng tra cứu 3 chiều thay cho hệ số nhân. Vì vậy, thiết kế này có thể được thực hiện bằng cách sử dụng các phần mềm như FPGA & Xilinx.

22). Chốt xung đẩy-kéo với điều kiện công suất thấp và tốc độ cao

Dự án này được sử dụng để thực hiện các chốt xung hiệu suất cao và tiết kiệm năng lượng chủ yếu được sử dụng cho các hệ thống VLSI bằng cách sử dụng cấu trúc liên kết mới. Bởi vì cấu trúc liên kết này chủ yếu phụ thuộc vào giai đoạn cuối cùng được điều khiển bằng cách sử dụng hai làn đường phân chia thông qua một bộ tạo xung có điều kiện.

23). Kiến trúc VLSI bộ mã số học trong SPIHT

Hệ thống được đề xuất này nâng cao thông lượng của phương pháp mã số học trong việc phân vùng tập hợp trong nén hình ảnh cây phân cấp (SPIHT) với kiến trúc tốc độ cao phụ thuộc vào FPGA.

24). Khử nhiễu tín hiệu điện tâm đồ dựa trên FPGA

Dự án này được sử dụng để chứa nhiễu trong tín hiệu ECG thông qua hai bộ lọc trung vị với kích thước điểm mẫu tương ứng là 91 & 7. Vì vậy, quá trình này có thể đạt được thông qua việc triển khai Thiết kế FPGA dựa trên mã VHDL.

25). Bộ xử lý chia tỷ lệ hình ảnh hiệu suất cao dựa trên VLSI với chi phí thấp

Dự án này được sử dụng để thực hiện một thuật toán cho bộ xử lý chia tỷ lệ hình ảnh dựa trên VLSI với ít bộ nhớ hơn và hiệu suất cao. Thiết kế hệ thống được đề xuất chủ yếu bao gồm việc kết hợp bộ lọc, các phương pháp động có thể cấu hình lại và chia sẻ phần cứng để giảm chi phí.

26). Thiết kế & triển khai kiến trúc mảng Systolic một cách hiệu quả

Ý tưởng chính của dự án này là thiết kế một mô hình phần cứng được sử dụng cho hệ số nhân mảng tâm thu. Mảng này có thể được sử dụng chủ yếu để thực hiện phép nhân nhị phân với sự trợ giúp của nền tảng VHDL. Thiết kế hệ thống được đề xuất có thể được thực hiện bằng phần mềm FPGA & Isim.

27). Thiết kế & Tổng hợp QPSK sử dụng Mã VHDL

QPSK là một trong những phương pháp điều chế chính. Phương pháp này được sử dụng trong các ứng dụng của đài vệ tinh. Kỹ thuật điều chế này có thể được thực hiện thông qua các cổng logic thuận nghịch. Việc thiết kế kỹ thuật QPSK có thể được thực hiện với sự trợ giúp của mã VHDL.

28). Thiết kế và triển khai bộ điều khiển DDR SDRAM với tốc độ cao

Hệ thống được đề xuất được sử dụng để thiết kế bộ điều khiển DDR SDRAM để truyền dữ liệu liên tục tùy thuộc vào tốc độ cao để đồng bộ hóa dữ liệu này giữa mạch của hệ thống nhúng và DDR SDRAM. Bằng cách sử dụng ngôn ngữ VHDL, mã có thể được phát triển.

29). Thiết kế và triển khai bộ xử lý RISC 32 Â-bit

Khái niệm chính của dự án này là thực hiện một 32 bit RISC (Máy tính Bộ hướng dẫn Giảm) với sự trợ giúp của một công cụ như XILINK VIRTEX4. Trong dự án này, 16 tập lệnh được thiết kế ở bất cứ nơi nào mọi lệnh có thể được thực hiện trong một chu kỳ CLK duy nhất bằng cách sử dụng phương pháp pipelining năm pha.

30). Thực hiện Cầu xe buýt giữa AHB và OCP

Hệ thống được đề xuất được sử dụng để thiết kế một cầu xe buýt giữa hai giao thức chung và tiêu chuẩn. Các giao thức truyền thông như AHB (Bus hiệu suất cao nâng cao) & OCP (Open Core Protocol) rất phổ biến được sử dụng trong các ứng dụng của SoC (Hệ thống trên chip) .

Dự án VLSI Ý tưởng cho Sinh viên Kỹ thuật

Dưới đây là danh sách các dự án VLSI dựa trên FPGA, MatLab, IEEE và Mini Projects dành cho sinh viên kỹ thuật.

Dự án VLSI dành cho sinh viên M. Tech

Danh sách các dự án VLSI dựa trên M. Tech Students bao gồm những điều sau đây.

- Thiết kế ô nhớ I0T dựa trên RHBD dựa trên RHBD hiệu quả và có độ tin cậy cao được sử dụng trong các ứng dụng hàng không vũ trụ

- Bộ dò pha với nửa tốc độ đa cấp được sử dụng cho mạch CLK & khôi phục dữ liệu

- Bộ so sánh với công suất thấp và tốc độ cao được sử dụng cho các ứng dụng chính xác

- Bộ dịch mức điện áp điều chỉnh với bộ ghép kênh tích hợp và hiệu suất cao

- Trình quảng cáo bậc ba dựa trên CNTFET với Hiệu suất cao

- Thiết kế so sánh độ lớn với công suất thấp

- Thiết kế cổng logic ngưỡng với chế độ hiện tại để phân tích độ trễ

- Thiết kế bộ giải mã dòng logic hỗn hợp với công suất thấp & hiệu suất cao

- Thiết kế khả năng kiểm tra logic của quy ước Sleep

- Bộ chuyển đổi mức điện áp cho các ứng dụng cung cấp kép với tốc độ cao và tiết kiệm điện

- Thiết kế và phân tích so sánh hai đuôi công suất thấp & điện áp thấp

- Thiết kế Flip-Flop dựa trên Xung kích hoạt với công suất thấp bằng phương pháp truyền tín hiệu

- Thiết kế mạch hiệu quả dựa trên FET có thể cấu hình lại thời gian chạy

- Thiết kế so sánh độ lớn với công suất thấp

- Phân tích độ trễ của thiết kế cổng logic với ngưỡng chế độ hiện tại

Các Dự án VLSI dựa trên FPGA cho sinh viên kỹ thuật và CMOS VLSI thiết kế các dự án nhỏ được liệt kê dưới đây.

- SEU Thiết kế và đặc tính mạch cứng cho FPGA dựa trên SRAM

- Một thiết kế LUT lai CMOS dựa trên bộ nhớ nhỏ gọn và ứng dụng tiềm năng được sử dụng trong FPGA

- Thực hiện dựa trên cảm biến siêu âm của FPGA để đo khoảng cách

- Triển khai FPGA cho Hệ số gian hàng với Spartan6 FPGA

- Biến đổi Wavelet rời rạc dựa trên Nâng với Spartan3 FPGA

- Bộ điều khiển ARM trong Robotics sử dụng FPGA

- UART dựa trên FPGA với Đa kênh

- Khử nhiễu tín hiệu điện tâm đồ bằng FPGA

- Triển khai FPGA dựa trên UTMI & Lớp giao thức USB 2.0

- Triển khai Bộ lọc Trung vị với Spartan3 FPGA

- Triển khai FPGA dựa trên thuật toán AES

- Hệ thống cảnh báo bảo mật dựa trên PIC để triển khai FPGA với Spartan 3an

- Triển khai FPGA để thiết kế bộ điều khiển cho hệ thống viễn thám

- Bộ xử lý hình ảnh của FPGA sử dụng Lọc hình ảnh tuyến tính & hình thái học

- Triển khai hình ảnh kết hợp y tế dựa trên Spartan3 FPGA

Danh sách của Các dự án nhỏ VLSI sử dụng mã VHDL bao gồm những điều sau đây.

- Bộ so sánh với tốc độ cao sử dụng VLSI

- Hệ số Floating-Point sử dụng VLSI

- Chuyển đổi từ nhị phân sang xám dựa trên VLSI

- Bộ lọc kỹ thuật số

- CLK Gating dựa trên VLSI

- Hệ số Vedic

- CMOS FF sử dụng VLSI

- Kiến trúc của Bộ xử lý song song sử dụng VLSI

- Trình quảng cáo đầy đủ dựa trên VLSI

- Thiết kế DRAM / Bộ nhớ truy cập ngẫu nhiên động dựa trên VLSI

- Bố cục SRAM dựa trên VLSI

- Bộ xử lý tín hiệu kỹ thuật số dựa trên VLSI

- Bộ ghép kênh dựa trên VLSI

- Thiết kế Đơn vị MAC dựa trên VLSI

- Bộ phân biệt dựa trên VLSI

- FFT dựa trên VLSI hoặc Biến đổi Fourier nhanh

- Kiến trúc của Biến đổi Cosine rời rạc dựa trên VLSI

- Thiết kế hệ số 16 bit sử dụng VLSI19

- Thiết kế dựa trên VLSI của FIFO Buffer

- Bộ tăng tốc tốc độ cao dựa trên VLSI

Dự án VLSI sử dụng MATLAB & Xilinx

Danh sách các dự án VLSI dựa trên MATLAB và Các dự án VLSI sử dụng Xilinx bao gồm những điều sau.

- Thiết kế & Phân tích Modem CDMA với MATLAB

- Thiết kế bộ lọc FIR sử dụng VHDL trên Phân tích dựa trên FPGA & MATLAB

- Mô phỏng dựa trên ModelSim & Matlab hoặc Simulink của Hệ thống cho Cơ khí Ô tô

- Các trình bổ sung dựa trên Xilinx như Ripple Carry & Carry Skip

- Đơn vị số học dựa trên Dấu chấm động 32-bit

- ALU dựa trên dấu chấm động

- Bộ xử lý RISC dựa trên 32-bit

- Khả năng chuyển đổi của mã trực giao

- Máy bán hàng tự động dựa trên Xilinx và Verilog

- Bộ cộng tiền tố song song dựa trên Xilinx với 256-bit

- Giao thức xác thực lẫn nhau bằng Xilinx

- Cấu trúc truy cập với chu trình đơn để kiểm tra logic bằng Xilinx

- UTMI & USB2.0 dựa trên Lớp giao thức sử dụng Xilinx

- Cấu hình nén và giải nén dữ liệu bằng Xilinx FPGA

- Xilinx 4000 dựa trên BIST & Spartan dựa trên FPGA

- Bộ lọc IIR dựa trên MATLAB & VLSI

- Bộ lọc FIR bằng MATLAB

Dự án IEEE

Các danh sách các Dự án IEEE VLSI được liệt kê bên dưới.

- Hệ thống tự động hóa gia đình không dây dựa trên VLSI sử dụng Bluetooth

- Loại bỏ nhiễu xung trong hình ảnh bằng cách sử dụng kiến trúc hiệu quả của VLSI

- Kiến trúc của một bộ xử lý trong bộ nhớ để nén đa phương tiện

- Giám sát hệ thống nhiệt độ bằng Cloud & IoT

- Triển khai hệ thống OFDM với IFFT & FFT

- Thiết kế & triển khai mã Hamming với Verilog

- Nhận dạng vân tay dựa trên VHDL sử dụng Bộ lọc Gabor

- Các hàm số học Ánh xạ với ROM tùy thuộc vào các phương pháp gần đúng

- Phân tích hiệu suất cao & hiệu suất mật độ thấp của bộ giải mã mã kiểm tra chẵn lẻ trong các ứng dụng công suất thấp

- Kiến trúc FFT với sự tiếp nhận của Pipelined Radix-2k

- Thiết kế Flip-Flops cho các ứng dụng VLSI sử dụng Công nghệ CMOS với hiệu suất cao

- Thiết kế bộ lọc FIR với Bảng tra cứu theo số học phân tán

- Bộ xử lý chia tỷ lệ hình ảnh nâng cao và chi phí thấp dựa trên VLSI

- Triển khai và thiết kế ASIC của Bộ mã hóa & giải mã Advance Turbo với 3GPP LTE

- Chốt xung đẩy-kéo với điều kiện công suất thấp và tốc độ cao

- Quét nâng cao trong thử nghiệm quét công suất thấp

- Kiến trúc VLSI bộ mã số học cho SPIHT

- Triển khai VHDL cho UART

- Bộ điều chỉnh điện áp dựa trên VLSI với mức sụt áp thấp

- Thiết kế Flash ADC với sơ đồ so sánh nâng cao

- Thiết kế hệ số nhân công suất thấp với kiểu logic liên tục độ trễ liên tục

- So sánh đuôi kép với hiệu suất cao và công suất thấp

- Hệ thống lưu trữ Flash với hiệu suất cao tùy thuộc vào bộ đệm ghi và bộ nhớ ảo

- FF công suất thấp dựa trên phương pháp tiếp cận ngăn xếp buồn ngủ

- Tối ưu hóa nguồn LFSR cho BIST công suất thấp Được triển khai trong HDL

- Thiết kế & Triển khai Máy bán hàng tự động với Verilog HDL

- Thiết kế Bộ tích lũy dựa trên Thế hệ của Mẫu 3 Trọng lượng với LP-LSFR

- Bộ giải mã Reed-Solomon với tốc độ cao và độ phức tạp thấp

- Kỹ thuật thiết kế hệ số nhân Dadda nhanh hơn

- Bộ thu dựa trên giải điều chế kỹ thuật số của Đài FM

- Tạo mẫu thử nghiệm với lược đồ BIST

- Triển khai kiến trúc VLSI với đường ống tốc độ cao

- Thiết kế giao thức OCP trên xe buýt trên chip sử dụng các chức năng của xe buýt

- Máy dò tần số pha & thiết kế bơm sạc được sử dụng cho vòng lặp bị khóa pha tần số cao

- Bộ nhớ Cache & Thiết kế bộ điều khiển Cache với VHDL

- Triển khai dựa trên ASTRAN của máy nén quảng cáo 3-2 & 4-2 công suất thấp

- Hệ thống thanh toán tiền điện trả trước sử dụng thiết kế trên chip

- Triển khai chồng chéo bằng cách sử dụng ô Logic & Phân tích sức mạnh của nó

- Thực hiện nhìn trước quảng cáo với Phân tích Hiệu suất Bit khác nhau bằng VHDL

- Thiết kế lớp liên kết dữ liệu với Wi-Fi MAC Giao thức

- Triển khai FPGA cho giao thức xác thực lẫn nhau với số học mô-đun

- Tạo tín hiệu PWM sử dụng FPGA & Chu kỳ nhiệm vụ thay đổi

Dự án thời gian thực

Danh sách của Dự án thời gian thực VLSI chủ yếu bao gồm các dự án nhỏ VLSI sử dụng mã VHDL và các dự án phần mềm VLSI cho sinh viên kỹ thuật ECE.

- Tích hợp thực dụng Bộ đệm hàng SRAM trong Kiến trúc DRAM 3-D không đồng nhất bằng cách sử dụng TSV

- Kỹ thuật Tự kiểm tra Tích hợp để Chẩn đoán Lỗi Độ trễ trong Mảng Cổng Lập trình Trường Dựa trên Cụm

- ASIC thiết kế hệ số phức hợp

- Triển khai VLSI chi phí thấp để loại bỏ hiệu quả tiếng ồn xung lực

- Dựa trên FPGA Véc tơ không gian PWM IC điều khiển cho ổ đĩa động cơ cảm ứng ba pha

- Thực hiện VLSI của Tự động tương quan và Thuật toán CORDIC cho mạng WLAN dựa trên OFDM

- Khai thác đường tự động bằng hình ảnh vệ tinh độ phân giải cao

- Thiết kế VHDL để Phân đoạn Hình ảnh Sử dụng Bộ lọc Gabor để Phát hiện Bệnh

- Kiến trúc bộ giải mã Turbo có độ phức tạp thấp cho mạng cảm biến không dây tiết kiệm năng lượng

- Cải thiện khả năng chuyển đổi mã trực giao bằng cách sử dụng triển khai FPGA

- Thiết kế và triển khai ALU dấu chấm động

- Thiết kế CORDIC cho góc quay cố định

- Mã sản phẩm Reed-Solomon để triển khai bộ điều khiển NAND Flash trên chip FPGA

- Cải thiện năng suất truy cập đọc SRAM thống kê bằng cách sử dụng mạch điện dung âm

- Quản lý nguồn của giao diện mạng MIMO trên hệ thống di động

- Thiết kế tiêu chuẩn mã hóa dữ liệu để mã hóa dữ liệu

- Công suất thấp và hiệu quả khu vực thực hiện Chọn quảng cáo

- Tổng hợp và triển khai UART bằng mã VHDL

- Kiến trúc được cải thiện cho Đơn vị cộng trừ dấu chấm động hợp nhất

- Máy phát 1-bit tất cả kỹ thuật số dựa trên FPGA sử dụng điều chế Delta-Sigma với đầu ra RF cho SDR

- Tối ưu hóa việc sử dụng chuỗi tìm kiếm trong Bộ giải mã BCH để truyền tỷ lệ lỗi cao

- Thiết kế kỹ thuật số của máy phát DS-CDMA sử dụng Verilog HDL và FPGA

- Thiết kế và triển khai kiến trúc mảng tâm thu hiệu quả

- Thuật toán học động lực học robot dựa trên VLSI

- Thiết kế đơn vị chức năng đa phương tiện linh hoạt sử dụng kỹ thuật triệt tiêu công suất giả

- Thiết kế Cầu xe buýt giữa AHB và OCP

- Tổng hợp hành vi của các mạch không đồng bộ

- Tối ưu hóa tốc độ của Bộ giải mã Viterbi được sửa đổi dựa trên FPGA

- Triển khai giao diện I2C

- Bộ nhân tốc độ cao / công suất thấp sử dụng kỹ thuật triệt tiêu công suất giả nâng cao

- Kẹp điện áp nguồn cung cấp ảo của mạch công suất để giảm rò rỉ hoạt động và độ tin cậy của cổng Oxit

- Bộ phân kênh hiệu quả năng lượng dựa trên FPGA cho đài phát thanh do phần mềm xác định

- Kiến trúc VLSI và tạo mẫu FPGA của một máy ảnh kỹ thuật số để bảo mật và xác thực hình ảnh

- Cải tiến hoạt động của Robot trong nhà

- Thiết kế và triển khai mạng hoán vị trên chip cho hệ thống đa xử lý trên chip

- Phương pháp đồng bộ hóa thời gian theo tốc độ mã vạch cho hệ thống OFDM không dây công suất thấp

- Bộ điều khiển DMA (Truy cập Bộ nhớ Trực tiếp) Sử dụng VHDL / VLSI

- FFT có thể cấu hình lại bằng cách sử dụng kiến trúc dựa trên CORDIC cho máy thu MIMI-OFDM

- Kỹ thuật triệt tiêu nguồn giả cho các ứng dụng Đa phương tiện / DSP

- Hiệu quả của mã BCH trong việc đánh dấu hình ảnh kỹ thuật số

- Bộ điều khiển SD-RAM tốc độ dữ liệu kép

- Triển khai bộ lọc Gabor để nhận dạng vân tay bằng Verilog HDL

- Thiết kế Dự phòng Quy mô Nanomet thực tế thông qua Thư viện Tế bào Tiêu chuẩn Aware để Dự phòng Cải thiện Thông qua 1 Tỷ lệ Chèn

- Một thuật toán nén và giải nén dữ liệu không mất dữ liệu và kiến trúc phần cứng của nó

- Khung sửa chữa các lỗi mềm nhiều bit

- Nén dữ liệu thử nghiệm hiệu quả dựa trên Viterbi

- Triển khai các khối FFT / IFFT cho OFDM

- Nén hình ảnh dựa trên Wavelet bằng mã hóa liên tục VLSI

- Thực hiện VLSI của Hệ số nhân hoàn toàn Pipelined Dưới 2d Kiến trúc DCT / IDCT cho Jpeg

- Mô phỏng lỗi dựa trên FPGA của các mạch tuần tự đồng bộ

Vì vậy, đây là tất cả về danh sách các dự án VLSI cho kỹ thuật, sinh viên M.Tech rất hữu ích trong việc lựa chọn chủ đề dự án năm cuối của họ. Sau khi dành thời gian quý báu của bạn khi xem qua danh sách này, chúng tôi tin rằng bạn đã có một ý tưởng khá tốt khi chọn chủ đề dự án mà bạn chọn từ danh sách các dự án của VLSI, và hy vọng rằng bạn có đủ tự tin để tiếp nhận bất kỳ chủ đề nào từ danh sách. Để biết thêm chi tiết và trợ giúp về các dự án này, bạn có thể viết thư cho chúng tôi trong phần nhận xét dưới đây. Đây là một câu hỏi dành cho bạn, VHDL là gì?

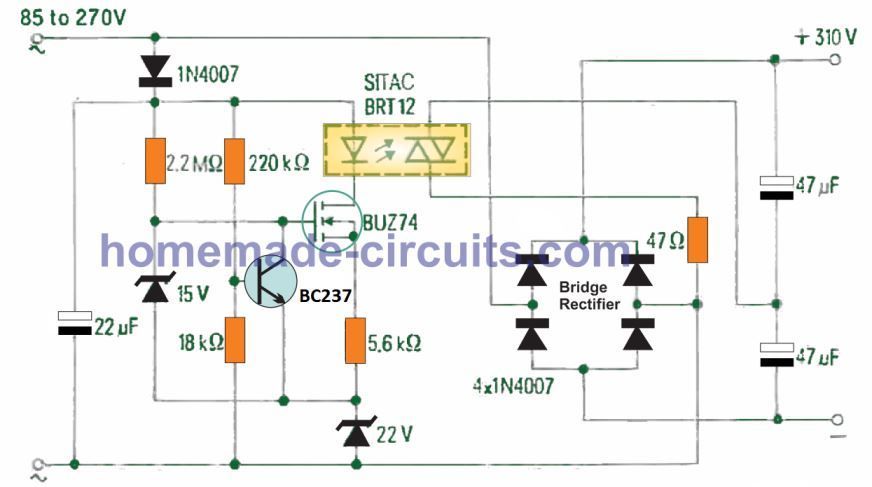

Tín dụng hình ảnh

- Dự án VLSI của công nghệ thiết lập