JTAG (Nhóm hành động thử nghiệm chung) là một tiêu chuẩn IEEE 1149.1 đã được thiết lập tốt, được phát triển vào năm 1980 để giải quyết các vấn đề sản xuất xảy ra trong bảng điện tử hoặc bo mạch in . Công nghệ này được sử dụng để cung cấp đủ quyền truy cập thử nghiệm cho từng bo mạch phức tạp khi quyền truy cập thử nghiệm đang giảm. Do đó, công nghệ quét ranh giới đã được đưa ra và tiêu chuẩn JTAG hoặc Đặc điểm kỹ thuật JTAG được thành lập. Độ phức tạp của thiết bị điện tử đang tăng lên từng ngày, vì vậy đặc điểm kỹ thuật JTAG đã trở thành định dạng thử nghiệm được chấp nhận để kiểm tra các thiết bị điện tử phức tạp và nhỏ gọn. Bài viết này thảo luận tổng quan về một JTAG giao thức - làm việc với các ứng dụng.

JTAG là gì?

Tên được đặt cho Cổng truy cập kiểm tra tiêu chuẩn IEEE 1149.1 cũng như Kiến trúc quét ranh giới được gọi là JTAG (Nhóm hành động kiểm tra chung). Kiến trúc quét ranh giới này chủ yếu được sử dụng trong máy tính bộ xử lý bởi vì bộ xử lý đầu tiên với JTAG đã được phát hành bởi Intel. Tiêu chuẩn IEEE này chỉ đơn giản xác định cách thức kiểm tra mạch của máy tính để xác nhận xem nó có hoạt động chính xác hay không sau quy trình sản xuất. Trên bảng mạch, các thử nghiệm được thực hiện để kiểm tra các mối hàn.

Nhóm Hành động Kiểm tra Chung cung cấp chế độ xem chân cắm cho người kiểm tra với mọi miếng đệm IC giúp xác định bất kỳ lỗi nào trong bảng mạch. Khi giao thức này được giao tiếp với chip, nó có thể gắn một đầu dò vào chip bằng cách cho phép nhà phát triển kiểm soát chip cũng như các kết nối của nó với các chip khác. Các nhà phát triển cũng có thể sử dụng giao diện với nhóm Hành động kiểm tra chung để sao chép phần sụn vào bộ nhớ không bay hơi trong một thiết bị điện tử.

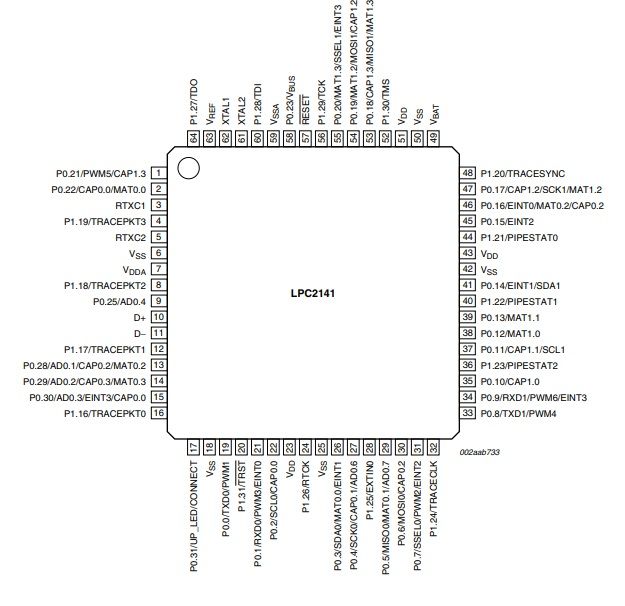

Cấu hình / Pin Out

Nhóm Hành động Kiểm tra Chung bao gồm 20 chân, trong đó mỗi chân và chức năng của nó được thảo luận dưới đây.

Pin1 (VTref): Đây là chân điện áp tham chiếu mục tiêu được sử dụng để kết nối với nguồn điện chính của mục tiêu nằm trong khoảng từ 1,5 đến 5,0VDC.

Pin2 (Vsupply): Đây là điện áp cung cấp mục tiêu được sử dụng để kết nối nguồn điện áp chính của mục tiêu 1.5VDC - 5.0VDC.

Pin3 (nTRST): Đây là chân đặt lại thử nghiệm được sử dụng để đặt lại trạng thái máy của bộ điều khiển TAP.

Các chân (4, 6, 8, 10, 12, 14, 16, 18 & 20): Đây là các chân GND thông thường.

Pin5 (TDI): Đây là dữ liệu thử nghiệm trong pin. Dữ liệu này được chuyển vào thiết bị mục tiêu. Ghim này phải được kéo lên theo một điều kiện xác định trên bảng mục tiêu.

Pin7 (TMS): Đây là chân Trạng thái Chế độ Kiểm tra được kéo để xác định điều kiện tiếp theo của máy trạng thái của bộ điều khiển TAP.

Pin9 (TCK): Đây là chân đồng hồ thử nghiệm đồng bộ hóa các hoạt động của máy trạng thái bên trong trong bộ điều khiển TAP.

Pin11 (RTCK): Đây là chân TCK của Input Return được sử dụng trong các thiết bị hỗ trợ xung nhịp thích ứng.

Pin13 (TDO): Đây là chân Kiểm tra Dữ liệu Ra, vì vậy dữ liệu được chuyển ra khỏi thiết bị mục tiêu vào Flyswatter.

Pin15 (nSRST): Đây là chân Thiết lập lại Hệ thống Mục tiêu được kết nối với tín hiệu thiết lập lại chính của mục tiêu.

Chân 17 & 19 (NC): Đây không phải là các chân kết nối.

JTAG đang hoạt động

Mục đích sử dụng ban đầu của JTAG là để kiểm tra ranh giới. Đây, là một bảng mạch in đơn giản bao gồm hai IC như CPU & FPGA . Một bảng thông thường có thể bao gồm nhiều IC. Nói chung, IC bao gồm nhiều chân được kết nối chung với nhiều kết nối. Ở đây, trong sơ đồ sau, chỉ có bốn kết nối được hiển thị.

Vì vậy, nếu bạn thiết kế nhiều bảng trong đó mỗi bảng có hàng nghìn kết nối. Trong đó, có một số bảng không tốt. Vì vậy chúng ta cần kiểm tra xem bo mạch nào hoạt động và bo mạch nào không hoạt động. Vì vậy, Nhóm Hành động Thử nghiệm Chung đã được thiết kế.

Giao thức này có thể sử dụng các chân điều khiển của tất cả các chip nhưng trong sơ đồ sau, Nhóm Hành động Kiểm tra Chung sẽ tạo tất cả các chân đầu ra của CPU & tất cả các chân đầu vào của FPGA. Sau đó, bằng cách truyền một số lượng dữ liệu từ các chân của CPU & đọc giá trị của các chân từ FPGA, JTAG nói rằng các kết nối của bảng mạch PCB vẫn ổn.

Trên thực tế, Nhóm Hành động Kiểm tra Chung bao gồm bốn tín hiệu logic TDI, TDO, TMS & TCK. Và những tín hiệu này cần được kết nối theo một cách cụ thể. Lúc đầu, TMS & TCK được kết nối song song với tất cả các IC của JTAG.

Sau đó, cả TDI & TDO được kết nối để tạo thành một chuỗi. Như bạn có thể quan sát, mỗi IC tuân thủ JTAG bao gồm 4 chân được sử dụng cho JTAG trong đó 3 chân là đầu vào và chân thứ 4 là đầu ra. Chân thứ năm như TRST là tùy chọn. Thông thường, các chân JTAG không được chia sẻ cho các mục đích khác.

Bằng cách sử dụng Nhóm hành động kiểm tra chung, tất cả các IC sử dụng kiểm tra ranh giới mà lý do ban đầu là do JTAG tạo ra. Hiện tại, việc sử dụng giao thức này đã được mở rộng để cho phép những thứ khác nhau như cấu hình FPGA và sau đó JTAG được sử dụng trong lõi FPGA cho mục đích gỡ lỗi.

Kiến trúc JTAG

Kiến trúc JTAG được hiển thị bên dưới. Trong kiến trúc này, tất cả các tín hiệu ở giữa logic lõi của thiết bị và các chân bị ngắt thông qua một đường quét nối tiếp được gọi là BSR hoặc Thanh ghi quét ranh giới. BSR này bao gồm các ‘tế bào’ quét ranh giới khác nhau. Nói chung, các ô quét ranh giới này không thể nhìn thấy nhưng chúng có thể được sử dụng để đặt hoặc đọc các giá trị trong chế độ kiểm tra từ các chân thiết bị.

Giao diện JTAG được gọi là TAP hoặc Cổng truy cập thử nghiệm sử dụng các tín hiệu khác nhau để hỗ trợ hoạt động quét ranh giới như TCK, TMS, TDI, TDO và TRST.

- Tín hiệu TCK hoặc Test Clock chỉ đơn giản là đồng bộ hóa các hoạt động bên trong của một cỗ máy trạng thái.

- TMS hoặc Tín hiệu chọn chế độ kiểm tra được lấy mẫu ở cạnh tăng của tín hiệu đồng hồ kiểm tra để quyết định trạng thái tiếp theo.

- Tín hiệu TDI hoặc Test Data In biểu thị dữ liệu được dịch chuyển vào thiết bị kiểm tra nếu không thì lập trình logic. Khi máy trạng thái bên trong ở trạng thái phù hợp thì nó được lấy mẫu ở cạnh tăng dần của TCK.

- Tín hiệu TDO hoặc Test Data Out biểu thị dữ liệu được dịch chuyển ra khỏi thiết bị kiểm tra nếu không lập trình logic. Khi máy trạng thái bên trong ở trạng thái phù hợp thì nó có giá trị trên cạnh giảm của TCK

- TRST hoặc Thử nghiệm Đặt lại là một chân tùy chọn được sử dụng để đặt lại máy trạng thái của bộ điều khiển TAP.

Bộ điều khiển TAP

Điểm truy cập thử nghiệm trong kiến trúc của JTAG bao gồm bộ điều khiển TAP, thanh ghi lệnh & thanh ghi dữ liệu thử nghiệm. Bộ điều khiển này bao gồm máy trạng thái thử nghiệm có trách nhiệm đọc các tín hiệu TMS & TCK. Ở đây, chân i / p dữ liệu đơn giản được sử dụng để tải dữ liệu vào các ô ranh giới giữa lõi IC và các chân vật lý, đồng thời cũng tải dữ liệu vào một trong các thanh ghi dữ liệu hoặc vào thanh ghi lệnh. Chân o / p dữ liệu được sử dụng để đọc dữ liệu từ các thanh ghi hoặc các ô ranh giới.

Máy trạng thái của bộ điều khiển TAP được điều khiển bởi TMS và nó được điều khiển bởi TCK. Máy trạng thái sử dụng hai đường dẫn để biểu thị hai chế độ khác nhau như chế độ hướng dẫn và chế độ dữ liệu.

Đăng ký

Có hai loại thanh ghi có sẵn trong quá trình quét ranh giới. Mọi thiết bị tuân thủ đều bao gồm tối thiểu hai thanh ghi dữ liệu trở lên và một thanh ghi lệnh.

Đăng ký chỉ dẫn

Thanh ghi lệnh được sử dụng để giữ lệnh hiện tại. Vì vậy, dữ liệu của nó được bộ điều khiển TAP sử dụng để quyết định những gì sẽ thực thi với các tín hiệu thu được. Thông thường, dữ liệu thanh ghi lệnh sẽ mô tả tín hiệu thanh ghi dữ liệu nào phải được chuyển tới.

Đăng ký dữ liệu

Các thanh ghi dữ liệu có sẵn ở ba loại là BSR (Thanh ghi quét ranh giới), thanh ghi BYPASS & ID CODES. Ngoài ra, các thanh ghi dữ liệu khác cũng có thể ở đó, tuy nhiên chúng không cần thiết như một phần tử của tiêu chuẩn JTAG.

Thanh ghi quét ranh giới (BSR)

BSR là thanh ghi dữ liệu thử nghiệm chính được sử dụng để chuyển dữ liệu từ và đến các chân I / O của thiết bị.

ĐƯỜNG VÒNG

Bypass là một thanh ghi bit đơn được sử dụng để truyền dữ liệu từ TDI - TDO. Vì vậy, nó cho phép các thiết bị bổ sung trong mạch được kiểm tra bằng chi phí tối thiểu.

MÃ ID

Loại thanh ghi dữ liệu này bao gồm mã ID cũng như số sửa đổi cho thiết bị. Vì vậy, dữ liệu này cho phép thiết bị được kết nối với tệp BSDL (Ngôn ngữ mô tả quét ranh giới) của nó. Tệp này bao gồm chi tiết cấu hình Quét ranh giới cho thiết bị.

Hoạt động của JTAG, ban đầu, chế độ lệnh được chọn trong đó một trong các trạng thái trong chế độ này ‘đường dẫn’ cho phép người vận hành đồng hồ trong một lệnh của TDI. Sau đó, máy trạng thái phát triển cho đến khi nó sắp xếp lại. Bước tiếp theo cho hầu hết các hướng dẫn là chọn chế độ dữ liệu. Vì vậy, trong chế độ này, dữ liệu được tải qua TDI để đọc từ TDO. Đối với TDI & TDO, các đường dẫn dữ liệu sẽ được sắp xếp theo hướng dẫn đã được cài đặt sẵn. Sau khi thực hiện xong thao tác đọc / ghi, một lần nữa máy trạng thái lại phát triển sang trạng thái đặt lại.

Sự khác biệt giữa JTAG Vs UART

Sự khác biệt giữa JTAG và UART bao gồm những điều sau đây.

| JTAG |

UART |

| Thuật ngữ “JTAG” là viết tắt của Nhóm Hành động Thử nghiệm Chung. | Thuật ngữ “ UART ”Là viết tắt của Universal Asynchronous Receiver / Transmitter. |

| Nó là một giao diện đồng bộ sử dụng phần cứng có sẵn để lập trình flash . | UART là một giao diện không đồng bộ sử dụng bộ nạp khởi động chạy trong bộ nhớ. |

| Nó là một tập hợp các cổng kiểm tra được sử dụng để gỡ lỗi nhưng cũng có thể được sử dụng để lập trình phần sụn (thường được thực hiện).

|

UART là một loại chip điều khiển các giao tiếp đến và đi từ một thiết bị, chẳng hạn như vi điều khiển, ROM, RAM, v.v. Thông thường, nó là một kết nối nối tiếp cho phép chúng ta giao tiếp với một thiết bị. |

| Chúng có sẵn trong bốn loại TDI, TDO, TCK, TMS & TRST. | Chúng có sẵn trong hai loại UART câm và FIFO UART. |

| Nhóm Hành động Kiểm tra Chung là lập trình nối tiếp hoặc giao thức truy cập dữ liệu được sử dụng trong giao diện của bộ vi điều khiển và các thiết bị liên quan. | UART là một loại chip, nếu không thì thành phần phụ của vi điều khiển được sử dụng để cung cấp phần cứng tạo luồng nối tiếp không đồng bộ như RS-232 / RS-485. |

| Các thành phần JTAG là Bộ xử lý, FPGA, CPLD , vân vân. | Các thành phần của UART là bộ tạo CLK, thanh ghi dịch chuyển I / O, bộ đệm truyền hoặc nhận, bộ đệm bus dữ liệu hệ thống, logic điều khiển đọc hoặc ghi, v.v. |

Trình phân tích giao thức JTAG

Trình phân tích giao thức JTAG như PGY-JTAG-EX-PD là một loại Trình phân tích giao thức bao gồm một số tính năng để nắm bắt và gỡ lỗi giao tiếp giữa máy chủ và thiết kế đang được thử nghiệm. Loại máy phân tích này là công cụ hàng đầu cho phép các kỹ sư kiểm tra và thiết kế kiểm tra các thiết kế cụ thể của JTAG cho các thông số kỹ thuật của nó thông qua việc sắp xếp PGY-JTAG-EX-PD như Master hoặc Slave để tạo ra lưu lượng JTAG & giải mã các gói giải mã của Giao thức Nhóm Hành động Kiểm tra Chung.

Đặc trưng

Các tính năng của bộ phân tích giao thức JTAG bao gồm những điều sau đây.

- Nó hỗ trợ lên đến 25MH tần số JTAG.

- Nó tạo ra lưu lượng và giải mã giao thức JTAG cho Bus đồng thời.

- Nó có JTAG Master Capability.

- JTAG có thể thay đổi Tốc độ dữ liệu & Chu kỳ nhiệm vụ.

- Độ trễ TDI & TCK do người dùng xác định.

- Máy tính chủ giao diện USB 2.0 hoặc 3.0.

- Phân tích lỗi trong giải mã giao thức

- Sơ đồ định thời bus được giải mã giao thức.

- Truyền dữ liệu giao thức liên tục tới máy tính chủ để cung cấp bộ đệm lớn.

- Danh sách hoạt động giao thức.

- Ở các tốc độ khác nhau, một kịch bản bài tập có thể được viết để kết hợp nhiều quá trình tạo khung dữ liệu.

Sơ đồ thời gian

Các sơ đồ thời gian của JTAG giao thức được hiển thị bên dưới. Trong sơ đồ sau, chân TDO vẫn ở trong điều kiện trở kháng cao ngoại trừ trong trạng thái bộ điều khiển shift-IR / shift-DR.

Trong điều kiện bộ điều khiển shift-IR & Shift-DR, chân TDO được cập nhật trên cạnh giảm của TCK thông qua Target và được lấy mẫu trên cạnh tăng của TCK thông qua Host.

Cả hai chân TDI & TMS đều được lấy mẫu đơn giản trên cạnh tăng dần của TCK thông qua Target. Đã cập nhật theo chiều hướng giảm nếu không thì TCK thông qua Máy chủ lưu trữ.

Các ứng dụng

Các Các ứng dụng JTAG bao gồm những điều sau đây.

- Nhóm Hành động Kiểm tra Chung thường được sử dụng trong Bộ xử lý để cung cấp quyền truy cập vào các chức năng mô phỏng hoặc gỡ lỗi của chúng.

- Tất cả các CPLD & FPGA đều sử dụng giao diện này làm giao diện để cấp quyền truy cập vào các chức năng lập trình của chúng.

- Nó được sử dụng để kiểm tra PCB mà không cần truy cập vật lý

- Nó được sử dụng cho các bài kiểm tra sản xuất cấp hội đồng quản trị.

Vì vậy, đây là tất cả về tổng quan về JTAG - cấu hình pin, làm việc với các ứng dụng. Tiêu chuẩn công nghiệp JTAG được sử dụng để xác minh thiết kế cũng như kiểm tra PCB sau khi sản xuất. Đây là một câu hỏi dành cho bạn, JTAG là viết tắt của?