Thuật ngữ CMOS là viết tắt của “Chất bán dẫn oxit kim loại bổ sung”. Đây là một trong những công nghệ phổ biến nhất trong ngành thiết kế chip máy tính và ngày nay nó được sử dụng rộng rãi để tạo thành mạch tích hợp trong nhiều ứng dụng khác nhau. Bộ nhớ máy tính, CPU và điện thoại di động ngày nay sử dụng công nghệ này do một số ưu điểm chính. Công nghệ này sử dụng cả thiết bị bán dẫn kênh P và kênh N. Một trong những công nghệ MOSFET phổ biến nhất hiện nay là công nghệ MOS bổ sung hoặc CMOS. Đây là công nghệ bán dẫn chiếm ưu thế cho vi xử lý, chip vi điều khiển, bộ nhớ như RAM, ROM, EEPROM và mạch tích hợp dành riêng cho ứng dụng (ASIC).

Giới thiệu về Công nghệ MOS

Trong thiết kế vi mạch, thành phần cơ bản và thiết yếu nhất là transistor. Vì vậy MOSFET là một loại bóng bán dẫn được sử dụng trong nhiều ứng dụng. Sự hình thành của bóng bán dẫn này có thể được thực hiện giống như một chiếc bánh sandwich bằng cách bao gồm một lớp bán dẫn, thường là một tấm wafer, một lát từ một tinh thể silicon một lớp silicon dioxide & một lớp kim loại. Các lớp này cho phép các bóng bán dẫn được hình thành bên trong vật liệu bán dẫn. Một chất cách điện tốt như Sio2 có một lớp mỏng với độ dày hàng trăm phân tử.

Các bóng bán dẫn mà chúng tôi sử dụng silicon đa tinh thể (poly) thay vì kim loại cho các phần cổng của chúng. Cổng Polysilicon của FET có thể được thay thế hầu như bằng cách sử dụng cổng kim loại trong các vi mạch quy mô lớn. Đôi khi, cả FET bằng polysilicon và kim loại đều được gọi là IGFET’s có nghĩa là FET có cổng cách điện, vì Sio2 bên dưới cổng là chất cách điện.

CMOS (Chất bán dẫn oxit kim loại bổ sung)

Chính lợi thế của CMOS so với NMOS và công nghệ BIPOLAR là công suất tiêu tán nhỏ hơn nhiều. Không giống như mạch NMOS hoặc BIPOLAR, mạch MOS bổ sung hầu như không có sự tiêu tán điện tĩnh. Nguồn chỉ bị tiêu tán trong trường hợp mạch thực sự chuyển mạch. Điều này cho phép tích hợp nhiều cổng CMOS trên một IC hơn trong NMOS hoặc công nghệ lưỡng cực , dẫn đến hiệu suất tốt hơn nhiều. Transistor bán dẫn oxit kim loại bổ sung bao gồm MOS kênh P (PMOS) và MOS kênh N (NMOS). Vui lòng tham khảo liên kết để biết thêm về quá trình chế tạo bóng bán dẫn CMOS .

CMOS (Chất bán dẫn oxit kim loại bổ sung)

NMOS

NMOS được xây dựng trên chất nền loại p với nguồn loại n và cống khuếch tán trên đó. Trong NMOS, phần lớn các hạt tải điện là electron. Khi một điện áp cao được đặt vào cổng, NMOS sẽ dẫn. Tương tự, khi một điện áp thấp được áp dụng cho cổng, NMOS sẽ không dẫn. NMOS được coi là nhanh hơn PMOS, vì các hạt tải điện trong NMOS, là các electron, di chuyển nhanh gấp đôi các lỗ trống.

Transistor NMOS

PMOS

MOSFET kênh P bao gồm Nguồn loại P và Xả khuếch tán trên đế loại N. Phần lớn chất mang là lỗ. Khi một điện áp cao được áp dụng cho cổng, PMOS sẽ không dẫn. Khi một điện áp thấp được áp dụng cho cổng, PMOS sẽ dẫn. Các thiết bị PMOS miễn nhiễm với tiếng ồn hơn các thiết bị NMOS.

Bóng bán dẫn PMOS

Nguyên tắc làm việc của CMOS

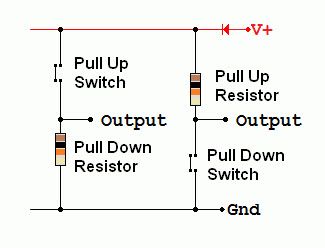

Trong công nghệ CMOS, cả hai bóng bán dẫn loại N và loại P đều được sử dụng để thiết kế các chức năng logic. Tín hiệu tương tự để BẬT một bóng bán dẫn của một loại được sử dụng để TẮT một bóng bán dẫn của loại khác. Đặc tính này cho phép thiết kế các thiết bị logic chỉ sử dụng các công tắc đơn giản, không cần điện trở kéo lên.

Trong CMOS cổng logic một tập hợp các MOSFET loại n được bố trí trong một mạng kéo xuống giữa đầu ra và đường ray cấp nguồn điện áp thấp (Vss hoặc khá thường xuyên nối đất). Thay vì điện trở tải của cổng logic NMOS, cổng logic CMOS có tập hợp các MOSFET loại p trong mạng kéo lên giữa đầu ra và đường ray điện áp cao hơn (thường được đặt tên là Vdd).

CMOS sử dụng Kéo lên & Kéo xuống

Do đó, nếu cả bóng bán dẫn loại p và loại n đều có cổng của chúng được kết nối với cùng một đầu vào, MOSFET loại p sẽ BẬT khi MOSFET loại n TẮT và ngược lại. Các mạng được sắp xếp sao cho một mạng BẬT và một mạng TẮT cho bất kỳ kiểu đầu vào nào như thể hiện trong hình bên dưới.

CMOS cung cấp tốc độ tương đối cao, tiêu tán điện năng thấp, biên độ nhiễu cao ở cả hai trạng thái và sẽ hoạt động trên nhiều loại điện áp nguồn và điện áp đầu vào (miễn là điện áp nguồn là cố định). Hơn nữa, để hiểu rõ hơn về nguyên lý hoạt động của Chất bán dẫn Oxit Kim loại Bổ sung, chúng ta cần thảo luận trong các cổng logic CMOS ngắn gọn như được giải thích bên dưới.

Thiết bị nào sử dụng CMOS?

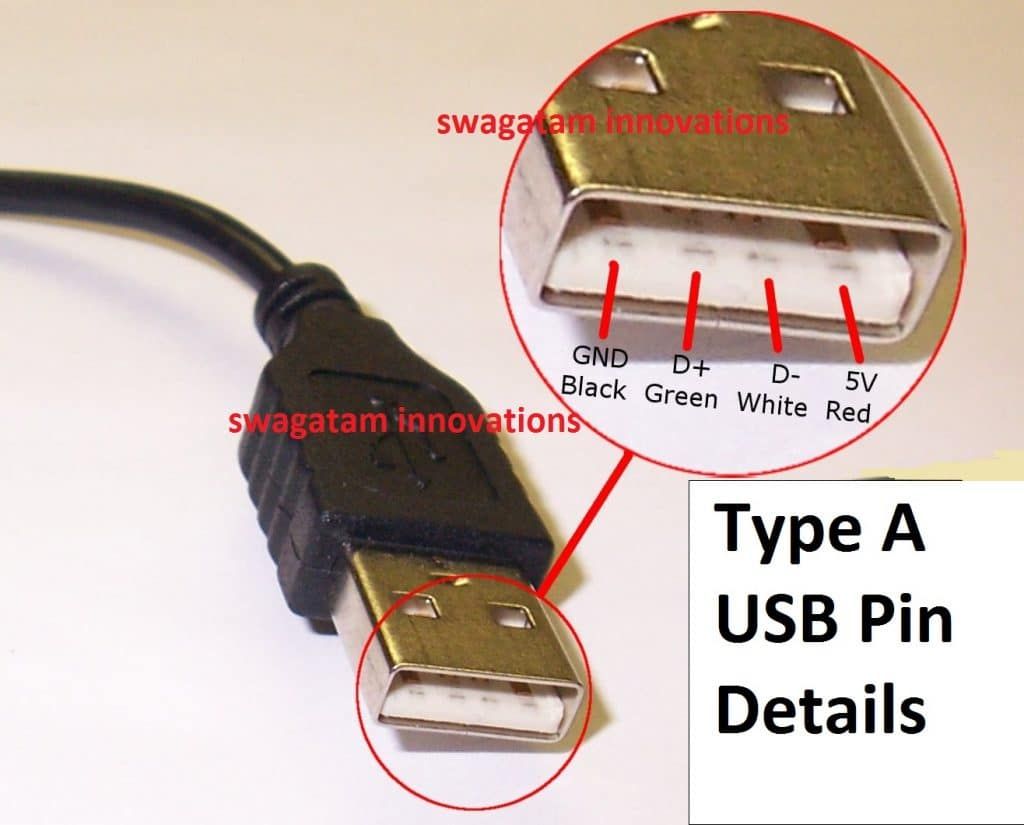

Công nghệ như CMOS được sử dụng trong các chip khác nhau như vi điều khiển, vi xử lý, SRAM (RAM tĩnh) và các mạch logic kỹ thuật số khác. Công nghệ này được sử dụng trong một loạt các mạch tương tự, bao gồm bộ chuyển đổi dữ liệu, cảm biến hình ảnh và bộ thu phát kết hợp cao cho một số loại giao tiếp.

Biến tần CMOS

Mạch nghịch lưu như hình bên dưới. Nó bao gồm PMOS và NMOS FET . Đầu vào A đóng vai trò là điện áp cổng cho cả hai bóng bán dẫn.

Bóng bán dẫn NMOS có đầu vào từ Vss (mặt đất) và bóng bán dẫn PMOS có đầu vào từ Vdd. Đầu cuối Y là đầu ra. Khi một điện áp cao (~ Vdd) được đưa ra tại cực đầu vào (A) của biến tần, PMOS trở thành mạch hở và NMOS chuyển sang TẮT vì vậy đầu ra sẽ được kéo xuống Vss.

Biến tần CMOS

Khi điện áp mức thấp ( Hình dưới đây cho thấy một cổng MOS NAND bổ sung 2 đầu vào. Nó bao gồm hai bóng bán dẫn NMOS nối tiếp giữa Y và Ground và hai bóng bán dẫn PMOS song song giữa Y và VDD. Nếu đầu vào A hoặc B là logic 0, ít nhất một trong các bóng bán dẫn NMOS sẽ TẮT, phá vỡ đường dẫn từ Y đến Đất. Nhưng ít nhất một trong các bóng bán dẫn pMOS sẽ được BẬT, tạo ra một đường dẫn từ Y đến VDD. Hai cổng NAND đầu vào Do đó, sản lượng Y sẽ cao. Nếu cả hai đầu vào đều ở mức cao, cả hai bóng bán dẫn nMOS sẽ BẬT và cả hai bóng bán dẫn pMOS sẽ TẮT. Do đó, đầu ra sẽ ở mức logic thấp. Bảng sự thật của cổng logic NAND được đưa ra trong bảng dưới đây. Cổng NOR 2 đầu vào được hiển thị trong hình bên dưới. Các bóng bán dẫn NMOS song song để kéo đầu ra xuống thấp khi một trong hai đầu vào ở mức cao. Các bóng bán dẫn PMOS mắc nối tiếp để kéo đầu ra cao khi cả hai đầu vào đều thấp, như được cho trong bảng dưới đây. Đầu ra không bao giờ được thả nổi. Cổng NOR hai đầu vào Bảng sự thật của cổng logic NOR được đưa ra trong bảng dưới đây. Việc chế tạo bóng bán dẫn CMOS có thể được thực hiện trên tấm silicon. Đường kính của tấm wafer từ 20mm đến 300mm. Về điều này, quá trình Lithography cũng giống như quá trình in ấn. Trên mỗi bước, các vật liệu khác nhau có thể được lắng đọng, khắc theo kiểu khác. Quá trình này rất đơn giản để hiểu bằng cách xem mặt trên của tấm wafer cũng như mặt cắt ngang trong một phương pháp lắp ráp đơn giản. Việc chế tạo CMOS có thể được thực hiện thông qua việc sử dụng ba công nghệ là N-well pt P-well, Twin well, một SOI (Silicon on Insulator). Vui lòng tham khảo liên kết này để biết thêm về Chế tạo CMOS . Tuổi thọ điển hình của pin CMOS là khoảng 10 năm. Tuy nhiên, điều này có thể thay đổi dựa trên việc sử dụng và môi trường xung quanh bất cứ nơi nào PC cư trú. Khi pin CMOS bị lỗi, máy tính không thể duy trì ngày và giờ chính xác trên máy tính sau khi tắt. Ví dụ: khi máy tính BẬT, bạn có thể thấy ngày và giờ như 12 giờ đêm & ngày 1 tháng 1 năm 1990. Lỗi này chỉ định rằng pin của CMOS bị lỗi. Các đặc điểm quan trọng nhất của CMOS là sử dụng công suất tĩnh thấp, khả năng chống ồn rất lớn. Khi bóng bán dẫn đơn từ cặp bóng bán dẫn MOSFET được TẮT thì tổ hợp nối tiếp sử dụng công suất đáng kể trong suốt quá trình chuyển đổi giữa hai bóng bán dẫn được nêu như BẬT & TẮT. Do đó, các thiết bị này không tạo ra nhiệt thải so với các loại mạch logic khác như logic TTL hoặc NMOS, thường sử dụng một số dòng điện đứng ngay cả khi chúng không thay đổi trạng thái của chúng. Các đặc điểm CMOS này sẽ cho phép tích hợp các chức năng logic với mật độ cao trên một mạch tích hợp. Do đó, CMOS đã trở thành công nghệ được sử dụng thường xuyên nhất trong các chip VLSI. Cụm từ MOS là tham chiếu đến cấu trúc vật lý của MOSFET bao gồm một điện cực có cổng kim loại nằm trên đỉnh của chất cách điện oxit bằng vật liệu bán dẫn. Một vật liệu như Nhôm chỉ được sử dụng một lần tuy nhiên vật liệu hiện nay là polysilicon. Việc thiết kế các cổng kim loại khác có thể được thực hiện bằng cách sử dụng sự trở lại thông qua sự xuất hiện của các vật liệu điện môi cao trong quá trình của quá trình CMOS. Các cảm biến hình ảnh như thiết bị kết hợp điện tích (CCD) và kim loại-oxit-bán dẫn bổ sung (CMOS) là hai loại công nghệ khác nhau. Chúng được sử dụng để chụp ảnh kỹ thuật số. Mỗi cảm biến hình ảnh đều có ưu điểm, nhược điểm và ứng dụng của nó. Sự khác biệt chính giữa CCD và CMOS là cách chụp khung hình. Một thiết bị tích điện như CCD sử dụng màn trập toàn cục trong khi CMOS sử dụng màn trập lăn. Hai cảm biến hình ảnh này thay đổi điện tích từ ánh sáng thành điện và xử lý nó thành tín hiệu điện tử. Quá trình sản xuất được sử dụng trong CCD là đặc biệt để hình thành khả năng di chuyển điện tích trên vi mạch mà không bị thay đổi. Vì vậy, quy trình sản xuất này có thể tạo ra các cảm biến chất lượng cực cao về độ nhạy sáng và độ trung thực. Ngược lại, chip CMOS sử dụng các quy trình sản xuất cố định để thiết kế chip và một quy trình tương tự cũng có thể được sử dụng để chế tạo bộ vi xử lý. Do sự khác biệt trong sản xuất, có một số điểm khác biệt rõ ràng giữa các cảm biến như CCD 7 CMOS. Cảm biến CCD sẽ chụp những hình ảnh ít nhiễu hơn và chất lượng rất lớn trong khi cảm biến CMOS thường dễ bị nhiễu hơn. Thông thường, CMOS sử dụng ít năng lượng hơn trong khi CCD sử dụng nhiều điện năng hơn cảm biến CMOS hơn 100 lần. Việc chế tạo chip CMOS có thể được thực hiện trên bất kỳ dây chuyền sản xuất Si điển hình nào vì chúng có xu hướng rất rẻ so với CCD. Cảm biến CCD đã trưởng thành hơn vì chúng được sản xuất hàng loạt trong thời gian dài. Cả máy ảnh CMOS & CCD đều phụ thuộc vào hiệu ứng của quang điện để tạo ra tín hiệu điện từ ánh sáng Dựa trên sự khác biệt trên, CCD được sử dụng trong máy ảnh để nhắm mục tiêu hình ảnh chất lượng cao thông qua nhiều pixel và độ nhạy sáng vượt trội. Thông thường, cảm biến CMOS có độ phân giải, chất lượng và độ nhạy kém hơn. Chốt lại có thể được định nghĩa là khi xảy ra ngắn mạch giữa hai cực như nguồn và đất để tạo ra dòng điện cao & IC có thể bị hỏng. Trong CMOS, latch-up là sự xuất hiện của đường mòn trở kháng thấp giữa đường ray điện & đường sắt mặt đất do giao tiếp giữa hai bóng bán dẫn như PNP & NPN ký sinh Linh kiện bán dẫn . Trong mạch CMOS, hai bóng bán dẫn như PNP & NPN được kết nối với hai đường cung cấp như VDD & GND. Việc bảo vệ các bóng bán dẫn này có thể được thực hiện thông qua các điện trở. Trong truyền dẫn chốt, dòng điện sẽ chạy thẳng từ VDD đến GND qua hai bóng bán dẫn để có thể xảy ra đoản mạch, do đó dòng điện cực đại sẽ chạy từ VDD đến cực nối đất. Có các phương pháp khác nhau để ngăn ngừa sự chậm trễ Trong phòng chống chốt, điện trở cao có thể được đặt trong đường mòn để ngăn dòng điện trong toàn bộ nguồn cung cấp & làm cho β1 * β2 dưới 1 bằng cách sử dụng các phương pháp sau. Cấu trúc của SCR ký sinh sẽ được bao bọc xung quanh các bóng bán dẫn như PMOS & NMOS thông qua một lớp oxit cách điện. Công nghệ bảo vệ chốt sẽ tắt thiết bị sau khi nhận thấy chốt. Các dịch vụ kiểm tra chốt có thể được thực hiện bởi nhiều nhà cung cấp trên thị trường. Việc kiểm tra này có thể được thực hiện bằng một chuỗi các nỗ lực để kích hoạt cấu trúc của SCR trong IC CMOS trong khi các chân liên quan được kiểm tra khi quá dòng chạy qua nó. Nên lấy những mẫu đầu tiên từ lô thử nghiệm và gửi chúng đến phòng thí nghiệm thử nghiệm của Latch-up. Phòng thí nghiệm này sẽ áp dụng nguồn điện tối đa có thể đạt được và sau đó cung cấp nguồn cung cấp hiện tại cho các đầu vào và đầu ra của chip bất cứ khi nào xảy ra Latch-up thông qua việc giám sát nguồn cung cấp hiện tại. Những lợi thế của CMOS bao gồm những điều sau đây. Lợi ích chính của CMOS so với TTL là độ ồn tốt cũng như tiêu thụ ít điện năng hơn. Điều này là do không có đường dẫn thẳng từ VDD đến GND, thời gian rơi dựa trên các điều kiện đầu vào, khi đó việc truyền tín hiệu kỹ thuật số sẽ trở nên dễ dàng và chi phí thấp thông qua chip CMOS. CMOS được sử dụng để giải thích dung lượng bộ nhớ trên bo mạch chủ của máy tính sẽ lưu trữ trong cài đặt của BIOS. Các cài đặt này chủ yếu bao gồm ngày, giờ và cài đặt phần cứng Kết quả đầu ra nếu CMOS hoạt động theo cả hai cách Những nhược điểm của CMOS bao gồm những điều sau đây. Các quy trình MOS bổ sung đã được triển khai rộng rãi và đã thay thế cơ bản các quy trình NMOS và lưỡng cực cho gần như tất cả các ứng dụng logic kỹ thuật số. Công nghệ CMOS đã được sử dụng cho các thiết kế vi mạch kỹ thuật số sau đây. Do đó, Bóng bán dẫn CMOS rất nổi tiếng vì chúng sử dụng năng lượng điện một cách hiệu quả. Họ không sử dụng nguồn cung cấp điện bất cứ khi nào họ thay đổi từ tình trạng này sang tình trạng khác. Ngoài ra, các chất bán dẫn miễn phí hoạt động lẫn nhau để dừng điện áp o / p. Kết quả là một thiết kế công suất thấp cung cấp ít nhiệt hơn, vì lý do này, các bóng bán dẫn này đã thay đổi các thiết kế khác trước đó như CCD trong cảm biến máy ảnh và được sử dụng trong hầu hết các bộ vi xử lý hiện tại. Bộ nhớ của CMOS trong máy tính là một loại RAM không bay hơi, lưu trữ cài đặt BIOS và thông tin ngày giờ. Tôi tin rằng bạn đã hiểu rõ hơn về khái niệm này. Hơn nữa, bất kỳ truy vấn nào liên quan đến khái niệm này hoặc dự án điện tử , hãy đóng góp ý kiến quý báu của bạn bằng cách bình luận trong phần bình luận bên dưới. Đây là một câu hỏi dành cho bạn, tại sao CMOS lại được ưu tiên hơn NMOS? ĐẦU VÀO ĐẦU VÀO LOGIC ĐẦU RA ĐẦU RA LOGIC 0 v 0 Vdd 1 Vdd 1 0 v 0 Cổng CMOS NAND

ĐẾN B Mạng kéo xuống Mạng kéo lên ĐẦU RA Y 0 0 TẮT TRÊN 1 0 1 TẮT TRÊN 1 1 0 TẮT TRÊN 1 1 1 TRÊN TẮT 0 Cổng CMOS NOR

ĐẾN B Y 0 0 1 0 1 0 1 0 0 1 1 0 Chế tạo CMOS

Tuổi thọ của Pin CMOS

Các triệu chứng lỗi của pin CMOS

Đặc điểm CMOS

CCD Vs CMOS

Trong một số ứng dụng, cảm biến CMOS gần đây đang được cải thiện đến mức gần như bình đẳng với các thiết bị CCD. Nói chung, máy ảnh CMOS không đắt và chúng có tuổi thọ pin cao.Cập nhật trong CMOS

Ưu điểm

TTL là một mạch logic kỹ thuật số nơi các bóng bán dẫn lưỡng cực hoạt động trên các xung DC. Một số cổng logic bóng bán dẫn thường được tạo thành từ một vi mạch duy nhất.Nhược điểm

Ứng dụng CMOS