Có một thời đại mà máy tính có kích thước khổng lồ đến mức để cài đặt chúng, dễ dàng cần một không gian phòng. Nhưng ngày nay chúng đã phát triển đến mức chúng ta thậm chí có thể mang chúng như một cuốn sổ ghi chép một cách dễ dàng. Sự đổi mới giúp điều này trở nên khả thi là khái niệm Mạch tích hợp. Trong Mạch tích hợp , một số lượng lớn hoạt động và yếu tố thụ động cùng với sự kết nối của chúng được phát triển trên một tấm silicon nhỏ thường có mặt cắt ngang 50 x 50 mils. Các quy trình cơ bản tiếp theo để sản xuất các mạch như vậy bao gồm tăng trưởng biểu mô, khuếch tán tạp chất bị che, tăng trưởng oxit và khắc oxit, sử dụng quang khắc để tạo mẫu.

Các thành phần trên tấm wafer bao gồm điện trở, bóng bán dẫn, điốt, tụ điện, v.v.… Phần tử phức tạp nhất để sản xuất trên IC là bóng bán dẫn. Bóng bán dẫn có nhiều loại chẳng hạn như CMOS, BJT, FET. Chúng tôi chọn loại công nghệ bóng bán dẫn được thực hiện trên vi mạch dựa trên các yêu cầu. Trong bài viết này, chúng ta hãy làm quen với khái niệm Chế tạo CMOS (hoặc) chế tạo bóng bán dẫn dưới dạng CMOS.

Chế tạo CMOS

Đối với yêu cầu tản nhiệt ít hơn Công nghệ CMOS được sử dụng để thực hiện các bóng bán dẫn. Nếu chúng ta yêu cầu một mạch nhanh hơn thì các bóng bán dẫn được thực hiện qua IC sử dụng BJT . Chế tạo Bóng bán dẫn CMOS vì IC có thể được thực hiện theo ba phương pháp khác nhau.

Công nghệ N-well / P-well, trong đó sự khuếch tán loại n được thực hiện trên chất nền loại p hoặc sự khuếch tán loại p được thực hiện trên chất nền loại n.

Các Công nghệ giếng đôi , Ở đâu NMOS và bóng bán dẫn PMOS được phát triển trên tấm wafer bằng cách khuếch tán đồng thời trên cơ sở tăng trưởng biểu mô, thay vì chất nền.

Quy trình silicon On Insulator, trong đó thay vì sử dụng silicon làm chất nền, vật liệu cách điện được sử dụng để cải thiện tốc độ và tính nhạy cảm của chốt.

Công nghệ N- well / P- well

CMOS có thể đạt được bằng cách tích hợp cả hai Bóng bán dẫn NMOS và PMOS trên cùng một tấm silicon. Trong công nghệ N-well, một giếng loại n được khuếch tán trên một chất nền loại p trong khi trong P- well thì nó là ngược lại.

Các bước chế tạo CMOS

Các Quy trình chế tạo CMOS lưu lượng được tiến hành bằng hai mươi bước chế tạo cơ bản trong khi được sản xuất bằng công nghệ N-well / P-well.

Tạo CMOS bằng N tốt

Bước 1: Đầu tiên ta chọn giá thể làm nền để chế tạo. Đối với giếng N, chất nền silicon loại P được chọn.

Cơ chất

Bước 2 - Quá trình oxy hóa: Sự khuếch tán có chọn lọc của các tạp chất loại n được thực hiện bằng cách sử dụng SiO2 như một rào cản bảo vệ các phần của tấm wafer khỏi sự nhiễm bẩn của chất nền. SiOhaiđược tạo ra bởi quá trình oxy hóa được thực hiện để bề mặt tiếp xúc với oxy và hydro chất lượng cao trong một buồng oxy hóa ở khoảng 10000c

oxy hóa

Bước 3 - Phát triển nhiếp ảnh gia: Ở giai đoạn này, để cho phép ăn mòn chọn lọc, lớp SiO2 phải chịu quá trình quang khắc. Trong quá trình này, tấm wafer được phủ một lớp màng đồng nhất của một loại nhũ tương cảm quang.

Sự phát triển của nhiếp ảnh gia

Bước 4 - Đắp mặt nạ: Bước này là bước tiếp tục của quá trình quang khắc. Trong bước này, một mẫu độ mở mong muốn được tạo ra bằng cách sử dụng một cây bút chì. Stencil này được sử dụng như một mặt nạ trên kính cản quang. Lớp nền bây giờ được tiếp xúc với tia UV chất cản quang hiện diện dưới các vùng tiếp xúc của mặt nạ bị polyme hóa.

Masking of Photoresist

Bước 5 - Loại bỏ Thợ chụp ảnh Không phơi sáng: Mặt nạ được tháo ra và vùng không tiếp xúc của photoresist được hòa tan bằng cách phát triển tấm wafer sử dụng một chất hóa học như Trichloroethylene.

Loại bỏ Photoresist

Bước 6 - Khắc: Tấm wafer được ngâm trong dung dịch ăn mòn của axit flohydric, dung dịch này loại bỏ oxit khỏi các khu vực mà chất pha tạp sẽ được khuếch tán.

Sự ăn mòn của SiO2

Bước 7 - Loại bỏ Toàn bộ Lớp Photoresist: Trong quá trình khắc , những phần SiO2 được bảo vệ bởi lớp cản quang sẽ không bị ảnh hưởng. Mặt nạ cản quang bây giờ được lột bỏ bằng dung môi hóa học (H2SO4 nóng).

Loại bỏ lớp photoresist

Bước 8 - Hình thành giếng N: Các tạp chất loại n được khuếch tán vào chất nền loại p qua vùng tiếp xúc, do đó tạo thành giếng N-.

Hình thành giếng N

Bước 9 - Loại bỏ SiO2: Lớp SiO2 bây giờ được loại bỏ bằng cách sử dụng axit flohydric.

Loại bỏ SiO2

Bước 10 - Lắng đọng Polysilicon: Sự sai lệch của cổng của một Bóng bán dẫn CMOS sẽ dẫn đến điện dung không mong muốn có thể gây hại cho mạch. Vì vậy, để ngăn chặn “Quá trình cổng tự liên kết” này được ưu tiên khi các vùng cổng được hình thành trước khi hình thành nguồn và thoát bằng cách sử dụng cấy ion.

Sự lắng đọng của Polysilicon

Polysilicon được sử dụng để hình thành cổng vì nó có thể chịu được nhiệt độ cao hơn 80000c khi tấm wafer phải chịu các phương pháp ủ để hình thành nguồn và cống. Polysilicon được gửi bằng cách sử dụng Quá trình lắng đọng hóa chất trên một lớp mỏng của ôxít cổng. Lớp oxit cổng mỏng này dưới lớp Polysilicon ngăn cản sự pha tạp thêm bên dưới vùng cổng.

Bước 11 - Hình thành Vùng Cổng: Ngoại trừ hai khu vực cần thiết để hình thành cổng cho Bóng bán dẫn NMOS và PMOS phần còn lại của Polysilicon bị loại bỏ.

Hình thành khu vực cổng

Bước 12 - Quá trình oxy hóa: Một lớp ôxy hóa được lắng đọng trên tấm wafer hoạt động như một lá chắn để tiếp tục quá trình khuếch tán và kim loại hóa .

Quá trình oxy hóa

Bước 13 - Đắp mặt nạ và khuếch tán: Để tạo ra các vùng khuếch tán tạp chất loại n bằng cách sử dụng quá trình che lấp các khoảng trống nhỏ được tạo ra.

Đắp mặt nạ

Sử dụng quá trình khuếch tán ba vùng n + được phát triển để hình thành các đầu cuối của NMOS.

N-khuếch tán

Bước 14 - Loại bỏ Oxit: Lớp oxit bị tước bỏ.

Loại bỏ oxit

Bước 15 - Khuếch tán loại P: Tương tự như sự khuếch tán loại n để hình thành các đầu cuối của sự khuếch tán loại p PMOS được thực hiện.

Khuếch tán loại P

Bước 16 - Rải oxit trường dày: Trước khi hình thành các đầu cuối kim loại, một oxit trường dày được tạo ra để tạo thành một lớp bảo vệ cho các vùng của tấm wafer mà không cần thiết bị đầu cuối.

Lớp oxit trường dày

Bước 17 - Kim loại hóa: Bước này được sử dụng để tạo ra các thiết bị đầu cuối kim loại có thể cung cấp kết nối với nhau. Nhôm được trải trên toàn bộ tấm wafer.

Kim loại hóa

Bước 18 - Loại bỏ kim loại thừa: Phần kim loại thừa được lấy ra khỏi tấm wafer.

Bước 19 - Hình thành các thiết bị đầu cuối: Trong các khoảng trống được hình thành sau khi loại bỏ các đầu cuối kim loại dư thừa được hình thành cho các kết nối.

Hình thành các thiết bị đầu cuối

Bước 20 - Gán tên đầu cuối: Tên được gán cho các thiết bị đầu cuối của Bóng bán dẫn NMOS và PMOS .

Gán tên thiết bị đầu cuối

Tạo CMOS bằng công nghệ P well

Quá trình p-well tương tự như quá trình N giếng ngoại trừ ở đây chất nền loại n được sử dụng và quá trình khuếch tán loại p được thực hiện. Để đơn giản, quy trình N giếng được ưu tiên hơn.

Chế tạo ống đôi của CMOS

Sử dụng quy trình Twin-tube, người ta có thể kiểm soát độ lợi của các thiết bị loại P và N. Các bước khác nhau liên quan đến chế tạo CMOS sử dụng phương pháp ống đôi như sau

- Chất nền loại n hoặc p được pha tạp nhẹ được lấy và sử dụng lớp biểu mô. Lớp biểu bì bảo vệ vấn đề chốt trong chip.

- Các lớp silicon có độ tinh khiết cao với độ dày đo được và nồng độ dopant chính xác được phát triển.

- Sự hình thành các ống cho giếng P và N.

- Cấu tạo oxit mỏng để bảo vệ khỏi bị nhiễm bẩn trong quá trình khuếch tán.

- Nguồn và cống được hình thành bằng phương pháp cấy ion.

- Các vết cắt được thực hiện để tạo các phần cho các tiếp điểm kim loại.

- Quá trình kim loại hóa được thực hiện để vẽ các điểm tiếp xúc kim loại

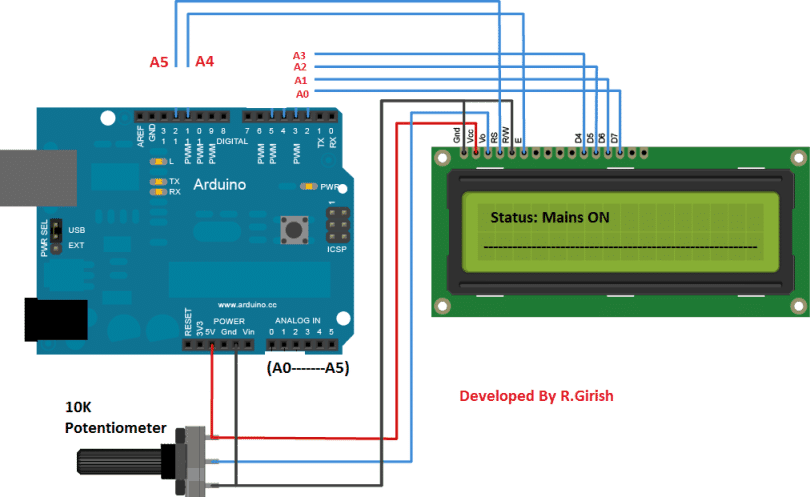

Bố cục IC CMOS

Khung cảnh phía trên của tới CMOS chế tạo và bố trí được đưa ra. Tại đây có thể quan sát rõ các điểm tiếp xúc kim loại khác nhau và sự khuếch tán N giếng.

Bố cục IC CMOS

Vì vậy, đây là tất cả về Kỹ thuật chế tạo CMOS . Chúng ta hãy xem xét một tấm wafer 1 trong hình vuông được chia thành 400 chip có diện tích bề mặt là 50 triệu x 50 triệu. Cần một diện tích là 50 triệu để chế tạo một bóng bán dẫn. Do đó mỗi IC chứa 2 bóng bán dẫn do đó có 2 x 400 = 800 bóng bán dẫn được xây dựng trên mỗi wafer. Nếu 10 tấm được xử lý mỗi lô thì 8000 bóng bán dẫn có thể được sản xuất đồng thời. Bạn đã quan sát thấy những thành phần khác nhau trên một vi mạch là gì?