Các mạch tổ hợp không sử dụng bất kỳ loại bộ nhớ nào. Do đó, vị trí trước đó của đầu vào không bao gồm bất kỳ kết quả nào đối với tình trạng hiện tại của mạch. Mặc dù, mạch tuần tự bao gồm bộ nhớ do đó đầu ra phụ thuộc vào đầu vào có nghĩa là đầu ra có thể thay đổi dựa trên đầu vào. Hoạt động của các mạch này có thể được thực hiện bằng cách sử dụng đầu vào mạch trước đó, CLK, bộ nhớ và đầu ra. Bài viết này thảo luận tổng quan về flip flop chủ-nô lệ. Nhưng trước khi tìm hiểu về chiếc flip-flop này, người ta phải biết những điều cơ bản về dép tông như flip flop SR và flip flop JK.

Master-Slave Flip Flop là gì?

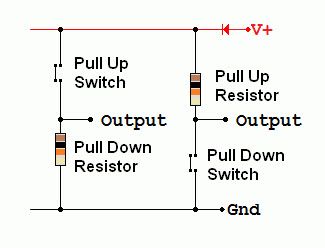

Về cơ bản, loại flip flop này có thể được thiết kế với hai JK FF bằng cách kết nối nối tiếp. Một trong những FF này, một FF hoạt động với tư cách chủ nhân cũng như các FF khác hoạt động như một nô lệ. Việc kết nối các FF này có thể được thực hiện như vậy, đầu ra của FF chủ có thể được kết nối với các đầu vào của FF phụ. Tại đây các đầu ra của FF phụ có thể được kết nối với đầu vào của FF chính.

Trong loại FF này, một biến tần cũng được sử dụng bổ sung cho hai FF. Kết nối biến tần có thể được thực hiện theo cách mà xung CLK đảo ngược có thể được kết nối với FF phụ. Nói cách khác, nếu xung CLK là 0 đối với FF chính, thì xung CLK sẽ là 1 đối với FF phụ. Tương tự, khi xung CLK là 1 đối với FF chính, thì xung CLK sẽ là 0 đối với FF phụ.

master-slave-flip-flop-mạch

Master-Slave FF làm việc

Bất cứ khi nào xung CLK tăng lên mức cao có nghĩa là 1, thì phụ có thể được tách ra, các đầu vào như J & K có thể thay đổi điều kiện của hệ thống.

FF phụ có thể được tách ra cho đến khi xung CLK xuống mức thấp có nghĩa là 0. Bất cứ khi nào xung CLK quay trở lại trạng thái thấp, thì dữ liệu có thể được truyền từ FF chính đến FF phụ và cuối cùng, o / p có thể được.

Lúc đầu, FF chính sẽ được kích hoạt ở mức tích cực trong khi FF phụ sẽ được kích hoạt ở mức âm. Vì lý do này, FF chính phản hồi trước.

Nếu J = 0 & K = 1, thì đầu ra của FF chính ‘Q’ sẽ chuyển đến đầu vào K của FF phụ & CLK buộc FF phụ phải RST (đặt lại), do đó FF phụ sẽ sao chép FF chính.

Nếu J = 1 & K = 0, thì FF chính ‘Q’ đi đến đầu vào J của FF phụ & chuyển tiếp âm của CLK đặt FF phụ và sao chép chính.

Nếu J = 1 & K = 1, thì nó chuyển đổi qua quá trình chuyển đổi tích cực của CLK và do đó, nô lệ sẽ chuyển đổi qua quá trình chuyển đổi tiêu cực của CLK.

Nếu cả J & K đều bằng 0 thì FF có thể cố định & Q không di chuyển được.

Sơ đồ thời gian

- Khi cả xung CLK & o / p của cái chính đều ở mức cao, thì nó vẫn ở mức cao cho đến khi CLK là thấp do trạng thái được lưu trữ.

- Hiện tại, o / p của chính biến thành thấp khi xung CLK một lần nữa chuyển thành cao và duy trì ở mức thấp cho đến khi CLK chuyển thành cao một lần nữa.

- Do đó chuyển đổi diễn ra trong một chu kỳ CLK.

thời gian-sơ đồ-of-a-master-slave-FF

- Bất cứ khi nào xung CLK là 1, cái chính được đặt nhưng không phải là phụ, do đó, o / p phụ vẫn là ‘0’ cho đến khi CLK vẫn là 1.

- Khi CLK ở mức thấp, sau đó nô lệ chuyển thành hoạt động & vẫn là '1' cho đến khi CLK lại chuyển thành '0'.

- Việc chuyển đổi diễn ra trong toàn bộ quy trình trong khi o / p đang thay đổi một lần trong một chu kỳ.

- Điều này làm cho flip flop này như một thiết bị đồng bộ vì nó chỉ truyền dữ liệu với thời gian tín hiệu CLK.

Vì vậy, đây là tất cả về Master-Slave Dep Lê . Từ những thông tin trên, cuối cùng, chúng ta có thể kết luận rằng FF này có thể được xây dựng với hai FF là master và slave. Khi một FF hoạt động giống như mạch chủ, nó sẽ kích hoạt trên cạnh hàng đầu của xung CLK. Tương tự, khi một FF khác hoạt động giống như mạch phụ, sau đó nó sẽ kích hoạt trên cạnh rơi của xung CLK.