Bài báo này giải thích tạo điều chế độ rộng xung tín hiệu với chu kỳ nhiệm vụ thay đổi trên FPGA sử dụng VHDL. PWM có tần số cố định và hiệu điện thế thay đổi được. Bài viết này cũng thảo luận về Trình quản lý đồng hồ kỹ thuật số để giảm tần số đồng hồ bằng cách giảm độ lệch của tín hiệu đồng hồ. Một tần số cố định được sử dụng để tạo ra dữ liệu đầu vào tạo ra tín hiệu PWM bằng cách sử dụng bộ so sánh. Các công ty điện tử thiết kế phần cứng dành riêng cho sản phẩm của họ với các tiêu chuẩn và giao thức của họ, điều này khiến người dùng cuối gặp khó khăn trong việc cấu hình lại phần cứng theo nhu cầu của họ. Yêu cầu này đối với phần cứng đã dẫn đến sự phát triển của một phân khúc khách hàng có thể cấu hình mới các mạch tích hợp lập trình trường được gọi là FPGA .

Điều chế độ rộng xung (PWM)

Điều chế độ rộng xung được sử dụng rộng rãi trong các ứng dụng truyền thông và hệ thống điều khiển . Điều chế độ rộng xung có thể được tạo ra bằng cách sử dụng các cách tiếp cận khác nhau trong hệ thống điều khiển. Ở đây, trong bài viết này, PWM được tạo bằng Ngôn ngữ Mô tả Phần cứng (VHDL) và được triển khai trên FPGA. Việc triển khai PWM trên FPGA có thể xử lý dữ liệu nhanh hơn và kiến trúc bộ điều khiển có thể được tối ưu hóa về không gian hoặc tốc độ.

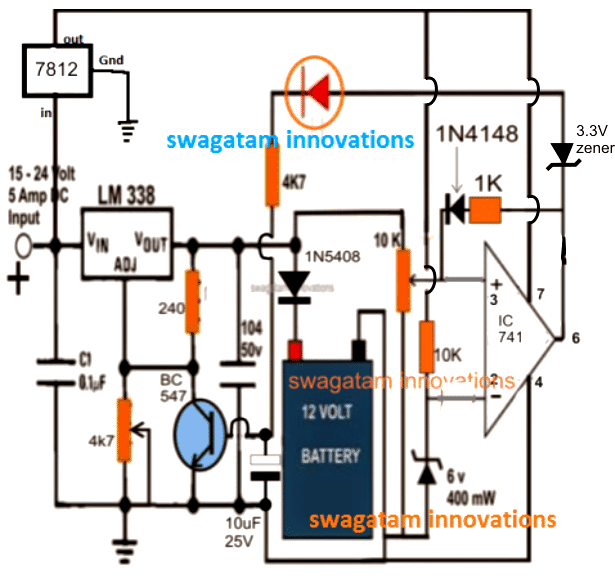

PWM là kỹ thuật cung cấp logic ‘0’ và logic ‘1’ trong một khoảng thời gian được kiểm soát. Nó là một nguồn tín hiệu liên quan đến việc điều chế chu kỳ nhiệm vụ của nó để kiểm soát lượng điện được gửi đến tải. Trong PWM, khoảng thời gian của sóng vuông được giữ không đổi và thời gian mà tín hiệu vẫn ở mức CAO là khác nhau.

PWM tạo ra các xung trên đầu ra của nó theo cách sao cho giá trị trung bình của HIGHs và LOWs tỷ lệ với đầu vào PWM. Chu kỳ hoạt động của tín hiệu có thể thay đổi. Tín hiệu PWM là một sóng vuông chu kỳ không đổi với chu kỳ nhiệm vụ thay đổi. Tức là, tần số của tín hiệu PWM là không đổi, nhưng khoảng thời gian của tín hiệu vẫn cao và thay đổi như hình bên.

Tín hiệu PWM

VHDL

VHDL là một ngôn ngữ, được sử dụng để mô tả hành vi của thiết kế mạch kỹ thuật số . VHDL được sử dụng bởi các ngành công nghiệp và học thuật cho mục đích mô phỏng các mạch kỹ thuật số. Thiết kế của nó có thể được mô phỏng và dịch theo dạng phù hợp để thực hiện trong phần cứng.

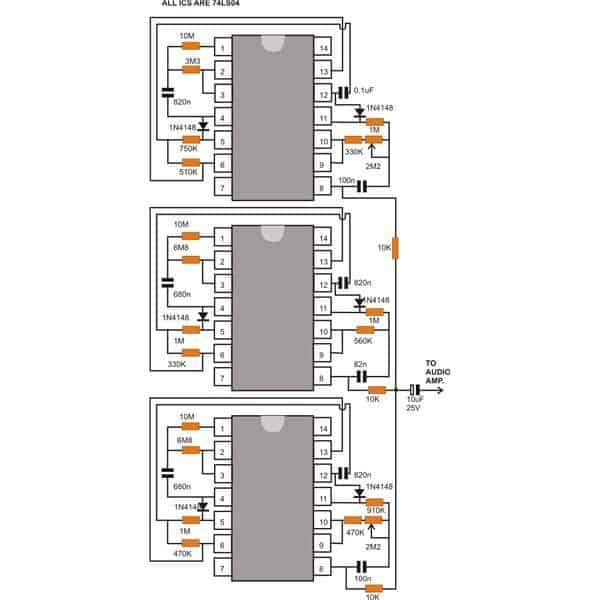

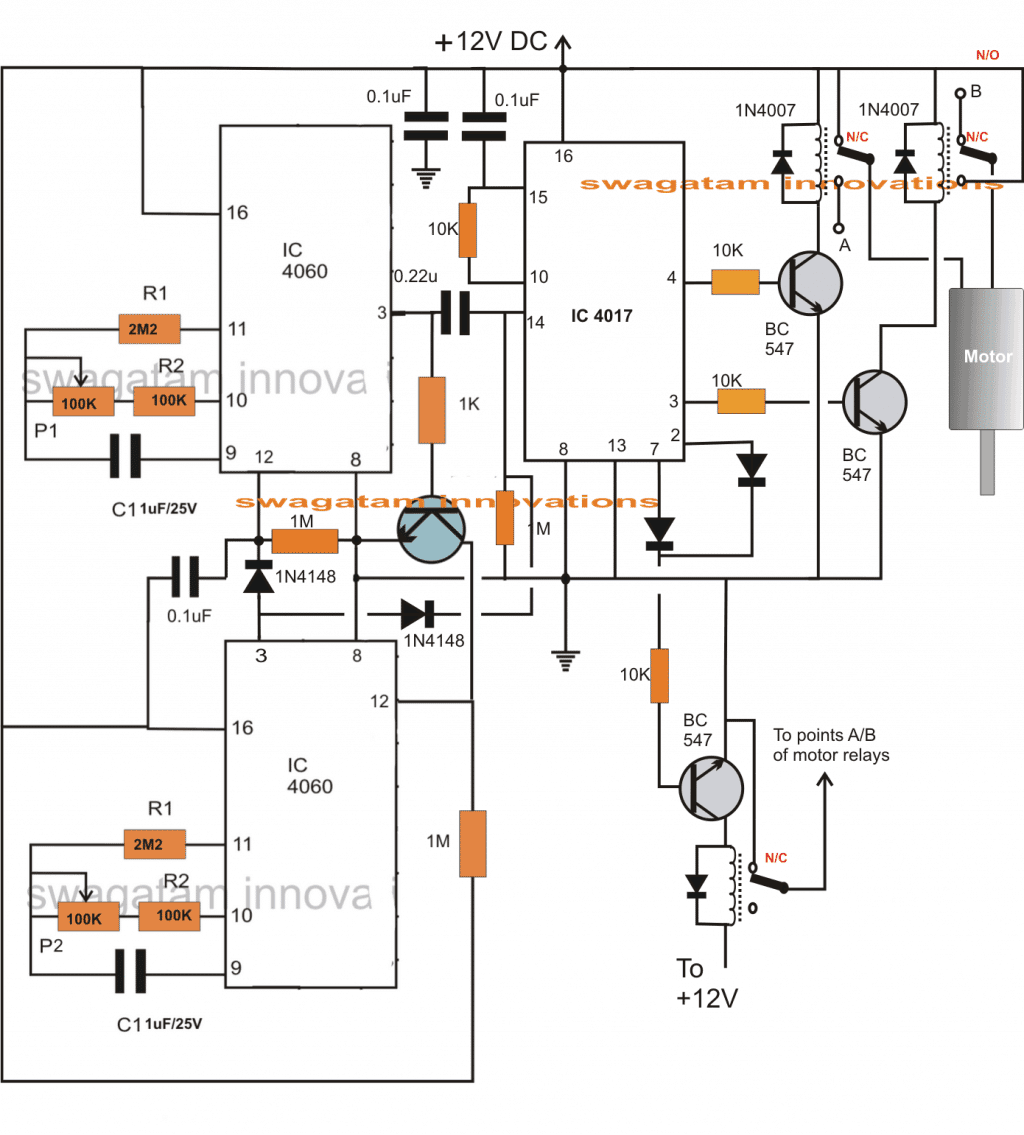

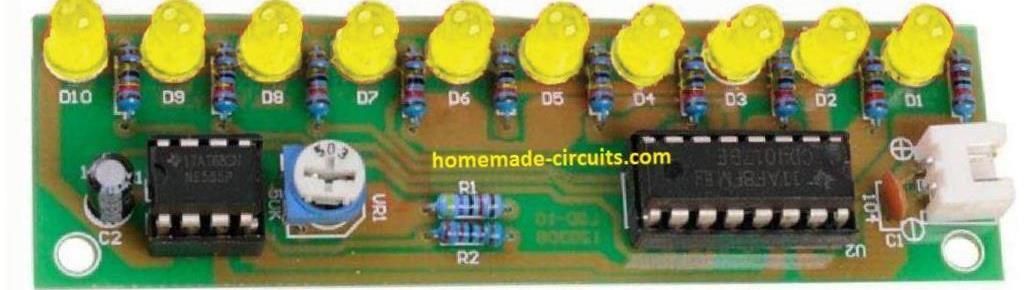

Kiến trúc PWM

Để sản xuất dữ liệu đầu vào để tạo PWM bằng cách sử dụng bộ đếm N-bit không chạy tốc độ cao, đầu ra của nó được so sánh với đầu ra của thanh ghi và lưu trữ chu kỳ nhiệm vụ đầu vào mong muốn với sự trợ giúp của bộ so sánh. Bộ so sánh đầu ra được đặt thành 1 khi cả hai giá trị này bằng nhau. Đầu ra của bộ so sánh này được sử dụng để đặt chốt RS. Tín hiệu tràn từ bộ đếm được sử dụng để thiết lập lại chốt RS. Các đầu ra của chốt RS cho đầu ra PWM mong muốn. Tín hiệu tràn này cũng được sử dụng để tải chu kỳ nhiệm vụ N-bit mới trong thanh ghi. PWM có tần số cố định và hiệu điện thế thay đổi được. Giá trị điện áp này thay đổi từ 0V đến 5 V.

Tín hiệu PWM với chu kỳ nhiệm vụ thay đổi

PWM cơ bản tạo ra các tín hiệu, cung cấp đầu ra của PWM, yêu cầu một bộ so sánh so sánh giữa hai giá trị. Giá trị đầu tiên đại diện cho tín hiệu hình vuông được tạo ra bởi bộ đếm N bit và giá trị thứ hai đại diện cho tín hiệu hình vuông chứa thông tin về chu kỳ nhiệm vụ. Bộ đếm tạo ra tín hiệu tải bất cứ khi nào có tràn. Khi tín hiệu tải trở nên hoạt động, thanh ghi sẽ tải giá trị chu kỳ nhiệm vụ mới. Tín hiệu tải cũng được sử dụng để đặt lại chốt. Đầu ra chốt là tín hiệu PWM. Điều này thay đổi theo sự thay đổi của giá trị chu kỳ nhiệm vụ.

FPGA là gì?

FPGA là Mảng cổng có thể lập trình trường. Nó là một loại thiết bị được sử dụng rộng rãi trong các mạch điện tử. FPGA là Thiết bị bán dẫn trong đó chứa các khối logic có thể lập trình và các mạch kết nối. Nó có thể được lập trình hoặc lập trình lại chức năng cần thiết sau khi sản xuất.

FPGA

Khái niệm cơ bản về FPGA

Khi một bảng mạch được sản xuất và nếu nó có chứa FPGA như một phần của nó. Điều này được lập trình trong quá trình sản xuất và hơn nữa có thể được lập trình lại sau đó để tạo bản cập nhật hoặc thực hiện các thay đổi cần thiết. Tính năng này của FPGA làm cho nó trở thành duy nhất của ASIC. Mạch tích hợp ứng dụng cụ thể (ASIC) được sản xuất tùy chỉnh cho nhiệm vụ thiết kế cụ thể. Trong quá khứ FPGA được sử dụng để phát triển tốc độ thấp, độ phức tạp và thiết kế âm lượng, nhưng ngày nay FPGA sẽ dễ dàng đẩy rào cản hiệu suất lên đến 500MHz.

Trong vi điều khiển, chip được thiết kế cho khách hàng và họ phải viết phần mềm và biên dịch nó thành tệp hex để tải lên vi điều khiển. Phần mềm này có thể dễ dàng thay thế vì nó được lưu trữ trong bộ nhớ flash. Trong FPGA, không có bộ xử lý nào để chạy phần mềm và chúng tôi là người thiết kế mạch. Chúng ta có thể cấu hình FPGA đơn giản như cổng AND hoặc phức tạp như bộ xử lý đa lõi. Để tạo một thiết kế, chúng tôi viết Ngôn ngữ mô tả phần cứng (HDL), có hai loại - Verilog và VHDL. Sau đó, HDL được tổng hợp thành một tệp bit bằng cách sử dụng BITGEN để cấu hình FPGA. FPGA lưu trữ cấu hình trong RAM, đó là cấu hình bị mất khi không có kết nối nguồn. Do đó, chúng phải được cấu hình mỗi khi cấp nguồn.

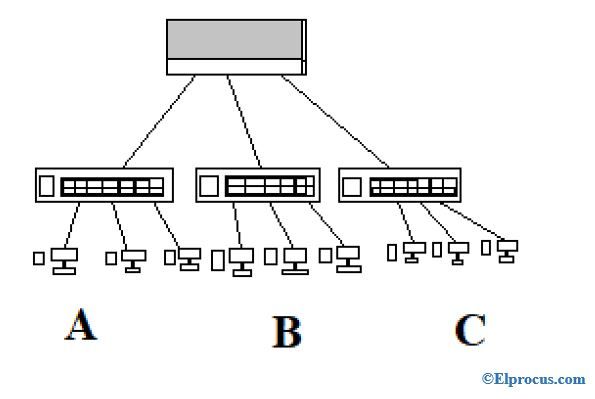

Kiến trúc của FPGA

FPGA là các chip silicon đúc sẵn có thể được lập trình bằng điện để thực hiện các thiết kế kỹ thuật số. FPGA dựa trên bộ nhớ tĩnh đầu tiên được gọi là SRAM được sử dụng để cấu hình cả logic và kết nối với nhau bằng cách sử dụng một dòng các bit cấu hình. EPGA hiện đại ngày nay chứa khoảng 3.30.000 khối logic và khoảng 1.100 đầu vào và đầu ra.

Kiến trúc FPGA

Kiến trúc của FPGA bao gồm ba thành phần chính

- Khối logic có thể lập trình, thực hiện các chức năng logic

- Định tuyến có thể lập trình (kết nối với nhau), thực hiện các chức năng

- Các khối I / O, được sử dụng để tạo các kết nối ngoài chip

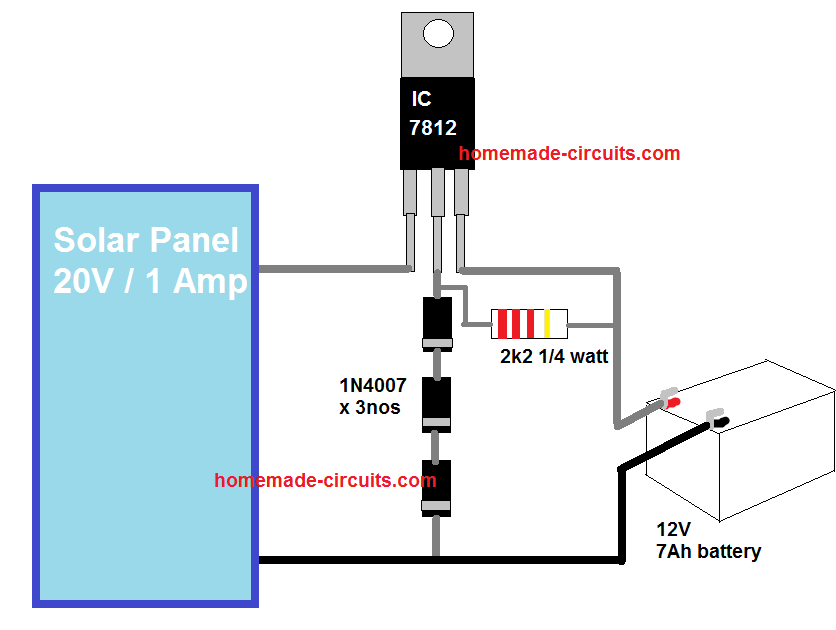

Các ứng dụng của tín hiệu PWM

Tín hiệu PWM được sử dụng rộng rãi cho các ứng dụng điều khiển. Như điều khiển động cơ DC, van điều khiển, máy bơm, thủy lực, v.v. Dưới đây là một vài ứng dụng của tín hiệu PWM.

- Hệ thống sưởi với thời gian chậm 10 đến 100Hz hoặc cao hơn.

- Động cơ điện DC 5 đến 10KHz

- Bộ nguồn hoặc bộ khuếch đại âm thanh 20 đến 200 KHz.

Bài báo này là tất cả về tạo tín hiệu PWM với chu kỳ nhiệm vụ thay đổi bằng cách sử dụng FPGA. Hơn nữa, đối với bất kỳ trợ giúp nào về các dự án điện tử hoặc nghi ngờ liên quan đến bài viết này, bạn có thể liên hệ với chúng tôi bằng cách bình luận ở phần bình luận được đưa ra bên dưới.