Bộ vi xử lý 8085 là một loại thiết bị bán dẫn được đồng bộ bởi CLK (đồng hồ). Bộ xử lý này có thể được xây dựng với các mạch logic điện tử được chế tạo bằng cách sử dụng các công nghệ như VLSI (tích hợp quy mô rất lớn) hoặc LSI (tích hợp quy mô lớn). Chức năng chính của bộ vi xử lý là thực hiện một số chức năng cũng như ra quyết định thay đổi chuỗi thực hiện chương trình. Trong máy tính, một đơn vị xử lý trung tâm sẽ được thực thi trên các bảng mạch đơn hoặc bổ sung để thực hiện các tác vụ tính toán. Có nhiều loại bộ vi xử lý khác nhau có sẵn trên thị trường như CPU, bao gồm mạch logic, khối điều khiển và nó có thể được tách thành ba phân đoạn như ALU, khối điều khiển và mảng thanh ghi.

Bộ vi xử lý 8085 là gì?

8085 bộ vi xử lý là một bộ xử lý đa dụng 8 bit có thể xử lý bộ nhớ 64K Byte. Bộ vi xử lý này bao gồm 40 chân cũng như hoạt động với + 5V Nguồn cấp . Bộ xử lý này có thể hoạt động ở tần số tối đa 3MHz. Bộ vi xử lý này có sẵn trong ba phiên bản như 8085 AH, 8085 AH1 và 8085 AH2 được thiết kế với công nghệ HMOS. Các phiên bản phát triển cao sử dụng 20% nguồn điện. Các tần số CLK của các phiên bản của bộ xử lý này là 8085 A- 3 MHz, 8085AH-3 MHz, 8085 AH2-5 MHz và 8085 AH1-6 MHz.

Bộ vi xử lý 8085

Cấu hình chân vi xử lý 8085

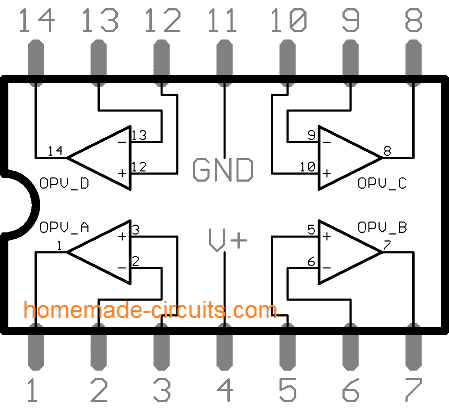

40 chân của bộ vi xử lý có thể được chia thành sáu nhóm như bus địa chỉ, bus dữ liệu, tín hiệu điều khiển & tín hiệu trạng thái cấp nguồn & tần số, tín hiệu khởi động bên ngoài và cổng đầu vào / đầu ra nối tiếp.

Cấu hình chân vi xử lý 8085

Xe buýt địa chỉ (A8-A15)

Các chân bus địa chỉ nằm trong khoảng từ A8 đến A15 và chúng chủ yếu áp dụng cho bit địa chỉ bộ nhớ đáng kể nhất.

Bus địa chỉ (hoặc) Bus dữ liệu (AD0-AD7)

Các chân bus địa chỉ hoặc chân bus dữ liệu nằm trong khoảng từ AD0 đến AD7, và các chân này có thể áp dụng cho LSB (các bit ít quan trọng nhất) của bus địa chỉ trong chu kỳ CLK của thiết bị chính cũng như được sử dụng làm bus dữ liệu cho chu kỳ xung nhịp thứ hai & chu kỳ đồng hồ thứ ba.

Một chu kỳ CLK có thể được thiết kế như, thời gian được sử dụng giữa hai xung lân cận của bộ dao động hoặc đơn giản là nó có thể đề cập đến 0 vôn. Ở đây xung nhịp đầu tiên là quá trình chuyển đổi chính của dải xung từ 0V đến 5V và sau đó quay trở lại 0V.

Kích hoạt chốt địa chỉ (ALE)

Về cơ bản, ALE hỗ trợ khử ghép kênh dữ liệu cũng như địa chỉ thứ tự thấp. Điều này sẽ tăng cao trong suốt chu kỳ đồng hồ chính cũng như cho phép các bit địa chỉ có thứ tự thấp. Bus địa chỉ với thứ tự thấp được thêm vào bộ nhớ nếu không có bất kỳ chốt bên ngoài nào.

Tín hiệu trạng thái (IO / 1000)

Tín hiệu trạng thái IO / M giải quyết xem địa chỉ dành cho bộ nhớ hay đầu vào / đầu ra. Khi địa chỉ ở mức cao thì địa chỉ của bus địa chỉ được sử dụng cho các thiết bị của thiết bị đầu vào / đầu ra. Khi địa chỉ ở mức thấp thì địa chỉ của bus địa chỉ được sử dụng cho bộ nhớ.

Tín hiệu trạng thái (S0-S1)

Các tín hiệu trạng thái S0, S1 đưa ra các chức năng cũng như trạng thái khác nhau dựa trên trạng thái của chúng.

- Khi S0, S1 là 01 thì hoạt động sẽ là HALT.

- S0, S1 là 10 thì hoạt động sẽ được VIẾT

- Khi S0, S1 là 10 thì hoạt động sẽ được ĐỌC

- Khi S0, S1 là 11 thì hoạt động sẽ FETCH

Tín hiệu thấp hoạt động (RD)

RD là một tín hiệu năng lượng thấp và một hoạt động được thực hiện bất cứ khi nào chỉ báo nhỏ, và nó được sử dụng để điều khiển hoạt động ĐỌC của bộ vi xử lý. Khi chân RD nhỏ đi thì bộ vi xử lý 8085 hiểu thông tin từ thiết bị I / O hoặc bộ nhớ.

Tín hiệu thấp hoạt động (WR)

Đây là một tín hiệu năng lượng thấp và nó kiểm soát hoạt động ghi của bộ vi xử lý. Bất cứ khi nào chân WR nhỏ đi, thì thông tin sẽ được ghi vào thiết bị I / O hoặc bộ nhớ.

SẴN SÀNG

Chân READY được sử dụng với bộ vi xử lý 8085 để đảm bảo thiết bị có được đặt để chấp nhận hoặc truyền dữ liệu hay không. Một thiết bị có thể là bộ chuyển đổi A / D hoặc màn hình LCD, v.v. Các thiết bị này được liên kết với bộ vi xử lý 8085 với chân READY. Khi chân này ở mức cao, thiết bị được chuẩn bị để truyền thông tin, nếu không có thì bộ vi xử lý sẽ ở lại cho đến khi chân này ở mức cao.

GIỮ

Chân HOLD chỉ định khi bất kỳ thiết bị nào yêu cầu sử dụng địa chỉ cũng như bus dữ liệu. Hai thiết bị là màn hình LCD cũng như bộ chuyển đổi A / D. Giả sử rằng nếu Công cụ chuyển đổi A / D đang sử dụng bus địa chỉ cũng như bus dữ liệu. Khi LCD mong muốn sử dụng cả hai bus bằng cách cung cấp tín hiệu HOLD, sau đó bộ vi xử lý sẽ truyền tín hiệu điều khiển về phía LCD sau đó chu kỳ hiện tại sẽ kết thúc. Khi nào màn hình LCD thủ tục kết thúc, sau đó tín hiệu điều khiển được truyền ngược lại đến bộ chuyển đổi A / D.

HLDA

Đây là tín hiệu phản hồi của HOLD, và nó chỉ định liệu tín hiệu này có thu được hay không. Sau khi lực cầu NẮM GIỮ thực hiện, tín hiệu này sẽ xuống thấp.

TRONG

Đây là một tín hiệu ngắt và mức độ ưu tiên của điều này trong số sự gián đoạn chậm. Tín hiệu này có thể được phép hoặc không được phép bởi phần mềm. Khi chân INTR lên cao thì bộ vi xử lý 8085 hoàn thành lệnh của dòng điện đang được thực thi và sau đó nhận ra tín hiệu INTR và tiến hành nó.

INTA

Khi bộ vi xử lý 8085 nhận được tín hiệu ngắt thì nó sẽ được nhận dạng. Điều này sẽ được thực hiện bởi INTA. Kết quả là khi ngắt sẽ được lấy thì INTA sẽ tăng cao.

RST 5.5, RST 6.5, RST 7.5

Các chân này là các ngắt có thể khởi động lại hoặc Vectored ngắt , được sử dụng để chèn một hàm khởi động lại bên trong lặp đi lặp lại. Tất cả các ngắt này đều có thể che được, chúng có thể được phép hoặc không được phép bằng cách sử dụng các chương trình.

BẨY

Cùng với bộ vi xử lý 8085 ngắt, TRAP là một ngắt không che được và nó không cho phép hoặc dừng bởi một chương trình. TRAP có quyền ưu tiên tối đa giữa các ngắt. Thứ tự ưu tiên từ tối đa đến thấp bao gồm TRAP, RST 5.5, RST 6.5, RST 7.5 và INTR.

ĐẶT LẠI

Chân RESET IN được sử dụng để đặt lại bộ đếm chương trình về 0 và sắp xếp lại kích hoạt ngắt cũng như HLDA dép tông (FF). Bộ xử lý trung tâm được giữ trong điều kiện RST cho đến khi chân này ở mức cao. Nhưng các thanh ghi cũng như cờ sẽ không bị hỏng ngoài thanh ghi lệnh.

RST (ĐẶT LẠI) RA NGOÀI

Chân RESET OUT chỉ định rằng đơn vị xử lý trung tâm đã được sắp xếp lại với RST IN.

X1 X2

Các đầu nối X1, X2 được kết hợp với bộ dao động bên ngoài để tạo ra hoạt động cần thiết cũng như hoạt động thích hợp của đồng hồ.

CLK

Đôi khi bắt buộc phải tạo ra CLK o / PS từ bộ vi xử lý 8085 để chúng có thể được sử dụng cho các thiết bị ngoại vi khác hoặc các mạch tích hợp kỹ thuật số khác. Điều này được cung cấp với pin CLK. Tần số của nó liên tục tương tự vì tần số mà bộ vi xử lý hoạt động.

SID

Đây là dữ liệu i / p nối tiếp và thông tin trên chân này được tải lên bit thứ 7 của bộ tích lũy trong khi lệnh RIM (Read Interrupt Mask) được thực hiện. RIM xác minh ngắt xem nó được che phủ hay không.

CỎ NHÂN TẠO

Đây là dữ liệu o / p nối tiếp và dữ liệu trên chân này sẽ gửi đầu ra của nó tới bit thứ 7 của bộ tích lũy bất cứ khi nào một lệnh của SIM được thực hiện.

VSS và VCC

VSS là chân nối đất trong khi Vcc là chân + 5v. Do đó Sơ đồ chân 8085 , cũng như các tín hiệu, được thảo luận chi tiết.

Vì vậy, đây là tất cả về bộ vi xử lý 8085 . Từ những thông tin trên, chúng ta có thể kết luận rằng tên thực của bộ vi xử lý này là 8085A. Bộ xử lý này là một thiết bị NMOS và bao gồm hàng nghìn bóng bán dẫn. Đây là một câu hỏi dành cho bạn, chức năng của Mức được kích hoạt ngắt trong bộ vi xử lý 8085?